www.ti.com

TMS320C6727,TMS320C6726,TMS320C6722

Floating-PointDigitalSignalProcessors

SPRS268E–MAY2005–REVISEDJANUARY2007

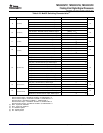

Table4-27.Additional

(1)

SPIMasterTimings,4-PinEnableOption

(2)(3)

NO.MINMAXUNIT

Polarity=0,Phase=0,

3P+15

toSPIx_CLKrising

Polarity=0,Phase=1,

0.5t

c(SPC)M

+3P+15

Delayfromslaveassertionof

toSPIx_CLKrising

17t

d(ENA_SPC)M

SPIx_ENAactivetofirstns

Polarity=1,Phase=0,

SPIx_CLKfrommaster.

(4)

3P+15

toSPIx_CLKfalling

Polarity=1,Phase=1,

0.5t

c(SPC)M

+3P+15

toSPIx_CLKfalling

Polarity=0,Phase=0,

0.5t

c(SPC)M

fromSPIx_CLKfalling

Polarity=0,Phase=1,

Maxdelayforslavetodeassert

0

fromSPIx_CLKfalling

SPIx_ENAafterfinalSPIx_CLK

18t

d(SPC_ENA)M

ns

edgetoensuremasterdoesnot

Polarity=1,Phase=0,

0.5t

c(SPC)M

beginthenexttransfer.

(5)

fromSPIx_CLKrising

Polarity=1,Phase=1,

0

fromSPIx_CLKrising

(1)TheseparametersareinadditiontothegeneraltimingsforSPImastermodes(Table4-25).

(2)P=SYSCLK2period

(3)FigureshowsonlyPolarity=0,Phase=0asanexample.Tablegivesparametersforallfourmasterclockingmodes.

(4)InthecasewherethemasterSPIisreadywithnewdatabeforeSPIx_ENAassertion.

(5)InthecasewherethemasterSPIisreadywithnewdatabeforeSPIx_ENAdeassertion.

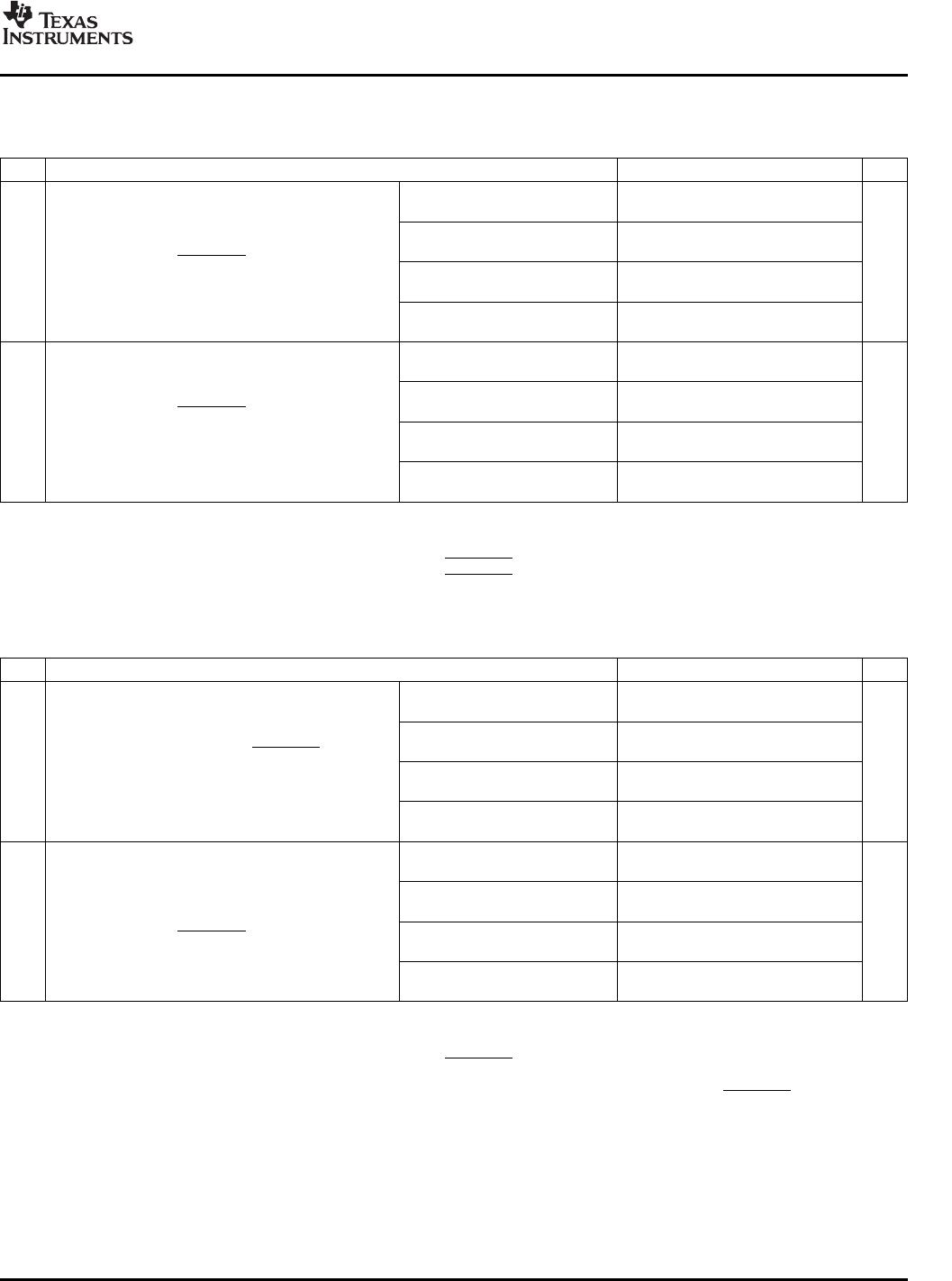

Table4-28.Additional

(1)

SPIMasterTimings,4-PinChipSelectOption

(2)(3)

NO.MINMAXUNIT

Polarity=0,Phase=0,

2P–10

toSPIx_CLKrising

Polarity=0,Phase=1,

0.5t

c(SPC)M

+2P–10

toSPIx_CLKrising

DelayfromSPIx_SCSactiveto

19t

d(SCS_SPC)M

ns

firstSPIx_CLK

(4)(5)

Polarity=1,Phase=0,

2P–10

toSPIx_CLKfalling

Polarity=1,Phase=1,

0.5t

c(SPC)M

+2P–10

toSPIx_CLKfalling

Polarity=0,Phase=0,

0.5t

c(SPC)M

fromSPIx_CLKfalling

Polarity=0,Phase=1,

0

DelayfromfinalSPIx_CLKedge

fromSPIx_CLKfalling

20t

d(SPC_SCS)M

tomasterdeassertingns

Polarity=1,Phase=0,

SPIx_SCS

(6)(7)

0.5t

c(SPC)M

fromSPIx_CLKrising

Polarity=1,Phase=1,

0

fromSPIx_CLKrising

(1)TheseparametersareinadditiontothegeneraltimingsforSPImastermodes(Table4-25).

(2)P=SYSCLK2period

(3)FigureshowsonlyPolarity=0,Phase=0asanexample.Tablegivesparametersforallfourmasterclockingmodes.

(4)InthecasewherethemasterSPIisreadywithnewdatabeforeSPIx_SCSassertion.

(5)ThisdelaycanbeincreasedundersoftwarecontrolbytheregisterbitfieldSPIDELAY.C2TDELAY[4:0].

(6)ExceptformodeswhenSPIDAT1.CSHOLDisenabledandthereisadditionaldatatotransmit.Inthiscase,SPIx_SCSwillremain

asserted.

(7)ThisdelaycanbeincreasedundersoftwarecontrolbytheregisterbitfieldSPIDELAY.T2CDELAY[4:0].

SubmitDocumentationFeedbackPeripheralandElectricalSpecifications85