www.ti.com

2.4InternalProgram/DataROMandRAM

00 20

2707

2F

2808

0F

3F

38

37

30

1F

18

10

17

3F

38

37

30

1F

18

17

10

2F

28

27

20

0F

08

00

07

Byte

ROM Page 1

Base Address

0x0004 0000

ROM Page 0

Base Address

0x0000 0000

Bank

0

Bank

1

Bank

2

Bank

3

13 33

10 30

17 37

14 34

1B 3B

18 38

1F 3F

1C 3C

RAM Page 0

Base Address

0x1000 0000

00 20

03 23

07

04

27

24

0B

08

2B

28

0F

0C

2F

2C

Byte

Bank

0

Bank

1

Bank

2

Bank

3

Bank

4

Bank

5

Bank

6

Bank

7

TMS320C6727,TMS320C6726,TMS320C6722

Floating-PointDigitalSignalProcessors

SPRS268E–MAY2005–REVISEDJANUARY2007

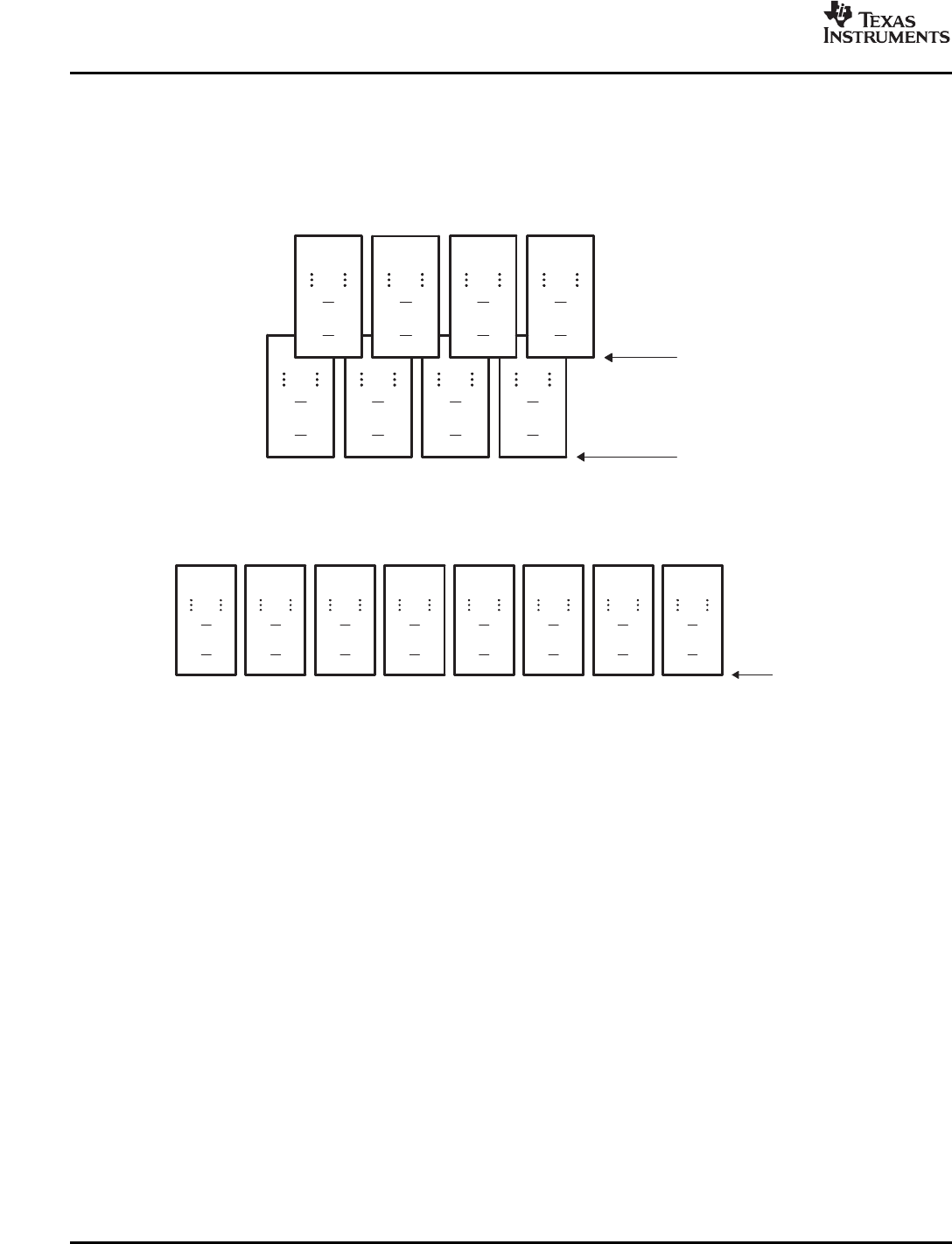

Theorganizationofprogram/dataROMandRAMonC672xissimpleandefficient.ROMisorganizedas

two256-bit-widepageswithfour64-bit-widebanks.RAMisorganizedasasingle256-bit-widepagewith

eight32-bit-widebanks.

TheinternalmemoryorganizationisillustratedinFigure2-2(ROM)andFigure2-3(RAM).

Figure2-2.Program/DataROMOrganization

Figure2-3.Program/DataRAMOrganization

TheC672xmemorycontrollersupportsuptothreeparallelaccessestotheinternalRAMandROMfrom

threeofthefollowingfoursourcesaslongastherearenobankconflicts:

•Two64-bitdataaccessesfromtheC67x+CPU

•One256-bit-wideprogramfetchfromtheprogramcache

•One32-bitdataaccessfromtheperipheralsystem(eitherdMAXorUHPI)

Aprogramcachemissis256bitswideandconflictsonlywithdataaccessestothesamepage.Multiple

dataaccessestodifferentpages,ortothesamepagebutdifferentbankswilloccurwithoutconflict.

TheorganizationoftheC672xinternalmemorysystemintomultiplepages(3total)andalargenumberof

banks(16total)meansthatitisstraightforwardtooptimizeDSPcodetoavoiddataconflicts.Several

factors,includingthelargeprogramcacheandthepartitioningofthememorysystemintomultiplepages,

minimizethenumberofprogramversusdataconflicts.

TheresultisanefficientmemorysystemwhichallowseasytuningtowardsthemaximumpossibleCPU

performance.

TheC672xROMconsistsofasoftwarebootloaderplusadditionalsoftware.Pleaserefertothe

C9230C100TMS320C672xFloating-PointDigitalSignalProcessorsROMDataManual(literaturenumber

SPRS277)formoredetailsontheROMcontents.

DeviceOverview 10SubmitDocumentationFeedback