www.ti.com

2.5ProgramCache

TMS320C6727,TMS320C6726,TMS320C6722

Floating-PointDigitalSignalProcessors

SPRS268E–MAY2005–REVISEDJANUARY2007

TheC672xDSPexecutescodedirectlyfromalargeon-chip32K-byteprogramcache.Theprogramcache

hasthesekeyfeatures:

•Wide256-bitpathtointernalROM/RAM

•Single-cycleaccessoncachehits

•2-cyclemisspenaltytointernalROM/RAM

•CachesexternalmemoryaswellasROM/RAM

•Direct-mapped

•Modes:Enable,Freeze,Bypass

•Softwareinvalidatetosupportcodeoverlay

Theprogramcachelinesizeis256bitswideandismatchedwitha256-bit-widepathbetweencacheand

internalmemory.Thisallowstheprogramcachetofillanentireline(correspondingtoeightC67x+CPU

instructions)withonlyasinglemisspenaltyof2cycles.

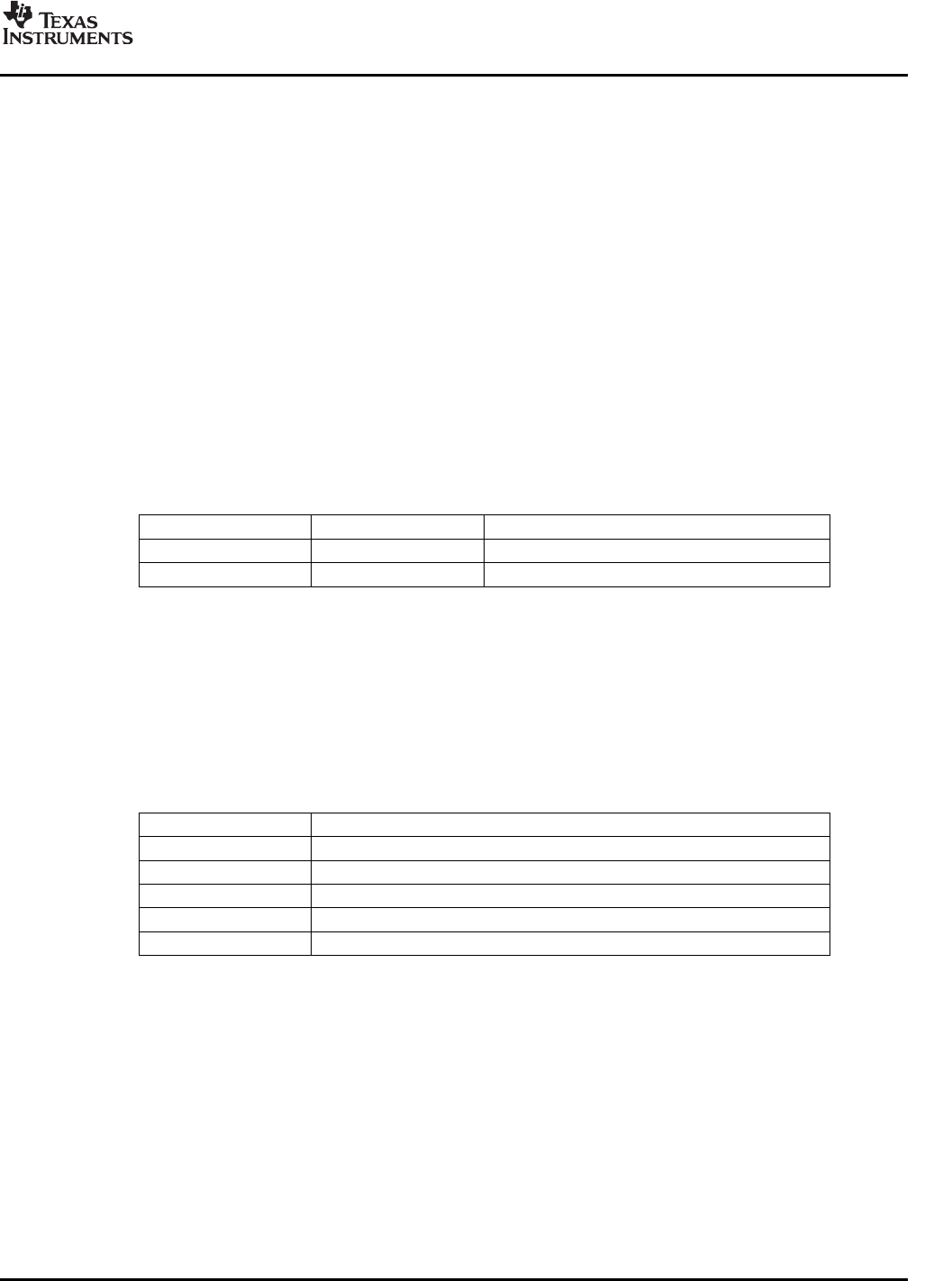

TheprogramcachecontrolregistersarelistedinTable2-4.

Table2-4.ProgramCacheControlRegisters

REGISTERNAMEBYTEADDRESSDESCRIPTION

L1PISAR0x20000000L1PInvalidateStartAddress

L1PICR0x20000004L1PInvalidateControlRegister

CAUTION

AnyapplicationwhichmodifiesthecontentsofprogramRAM(forexample,aprogram

overlay)mustinvalidatetheaddressesfromprogramcachetomaintaincoherencyby

explicitlywritingtotheL1PISARandL1PICRregisters.

TheCacheMode(Enable,Freeze,Bypass)isconfiguredthroughaCPUinternalregister(CSR,bits7:5).

TheseoptionsarelistedinTable2-5.Typically,onlytheCacheEnableModeisused.Butadvancedusers

mayutilizeFreezeandBypassmodestotuneperformance.

Table2-5.CacheModesSetThroughPCCFieldofCSRCPURegisteronC672x

CPUCSR[7:5]CACHEMODE

000bEnable(Deprecated-MeansdirectmappedRAMonsomeC6000devices)

010bEnable-Cacheisenabled,cachemissescausealinefill.

011bFreeze-Cacheisenabled,butcontentsareunchangedbymisses.

100bBypass-Forcescachemisses,cachecontentsfrozen.

OtherValuesReserved-NotSupported

CAUTION

AlthoughtheresetvalueofCSR[7:5](PCCfield)is000b,thevaluemaybemodified

duringthebootprocessbytheROMcode.RefertotheappropriateROMdatasheet

formoredetails.However,notethatthecachemaybedisabledwhencontrolis

actuallypassedtoapplicationcode.Therefore,itmaybenecessarytowrite'010b'to

thePCCfieldtoexplicitlyenablethecacheatthestartofapplicationcode.

CAUTION

ChangingthecachemodethroughCSR[7:5]doesnotinvalidateanylinesalreadyin

thecache.Toinvalidatethecacheaftermodificationsaremadetoprogramspace,the

controlregistersL1PISARandL1PICRmustbeused.

SubmitDocumentationFeedbackDeviceOverview11