www.ti.com

3DeviceConfigurations

3.1DeviceConfigurationRegisters

3.2PeripheralPinMultiplexingOptions

TMS320C6727,TMS320C6726,TMS320C6722

Floating-PointDigitalSignalProcessors

SPRS268E–MAY2005–REVISEDJANUARY2007

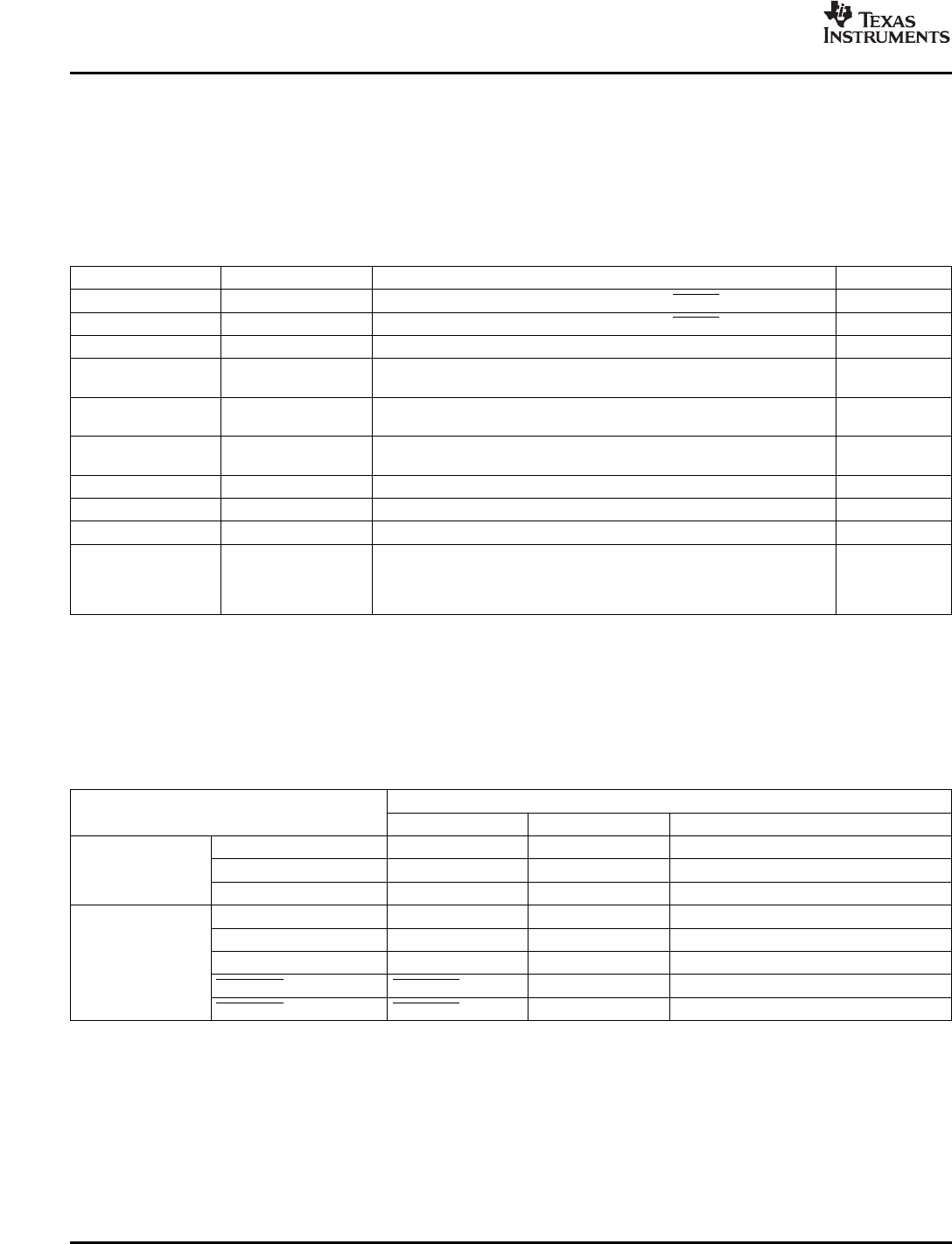

TheC672xDSPincludesseveraldevice-levelconfigurationregisters,whicharelistedinTable3-1.These

registersneedtobeprogrammedaspartofthedeviceinitializationprocedure.SeeSection3.2.

Table3-1.Device-LevelConfigurationRegisters

REGISTERNAMEBYTEADDRESSDESCRIPTIONDEFINED

CFGPIN00x40000000CapturesvaluesofeightpinsonrisingedgeofRESETpin.Table2-10

CFGPIN10x40000004CapturesvaluesofeightpinsonrisingedgeofRESETpin.Table2-11

CFGHPI0x40000008ControlsenableofUHPIandselectionofitsoperatingmode.Table4-12

CFGHPIAMSB0x4000000CControlsupperbyteofUHPIaddressintoC672xaddressspaceinTable4-13

Non-MultiplexedModeorifexplicitlyenabledforsecuritypurposes.

CFGHPIAUMB0x40000010ControlsuppermiddlebyteofUHPIaddressintoC672xaddressspaceTable4-14

inNon-MultiplexedModeorifexplicitlyenabledforsecuritypurposes.

CFGRTI0x40000014SelectsthesourcesfortheRTIInputCapturesfromamongthesixTable4-37

McASPDMAevents.

CFGMCASP00x40000018SelectstheperipheralpintobeusedasAMUTEIN0.Table4-19

CFGMCASP10x4000001CSelectstheperipheralpintobeusedasAMUTEIN1.Table4-20

CFGMCASP2

(1)

0x40000020SelectstheperipheralpintobeusedasAMUTEIN2.Table4-21

CFGBRIDGE0x40000024ControlsresetofthebridgeBR2inFigure2-4.ThisbridgemustberesetTable2-7

explicitlyafteranychangetothePLLcontrolleraffectingSYSCLK1and

SYSCLK2andbeforethedMAXorUHPIaccessestheCPUSlavePort

(CSP).

(1)CFGMCASP2isreservedontheC6722.

ThissectiondescribestheoptionsforconfiguringperipheralswhichsharepinsontheC672xDSP.

Table3-2liststheoptionsforconfiguringtheSPI0,I2C0,andI2C1peripheralpins.

Table3-2.OptionsforConfiguringSPI0,I2C0,andI2C1

CONFIGURATION

OPTION1OPTION2OPTION3

PERIPHERALSPI03-,4,-or5-pinmode3-pinmodedisabled

I2C0disableddisabledenabled

I2C1disabledenabledenabled

PINSSPI0_SOMI/I2C0_SDASPI0_SOMISPI0_SOMII2C0_SDA

SPI0_SIMOSPI0_SIMOSPI0_SIMOGPIOthroughSPI0_SIMOpincontrol

SPI0_CLK/I2C0_SCLSPI0_CLKSPI0_CLKI2C0_SCL

SPI0_SCS/I2C1_SCLSPI0_SCSI2C1_SCLI2C1_SCL

SPI0_ENA/I2C1_SDASPI0_ENAI2C1_SDAI2C1_SDA

DeviceConfigurations 30SubmitDocumentationFeedback