www.ti.com

Registers

3.5 I2C Data Count Register (ICCNT)

The I2C data count register (ICCNT) is used to indicate how many data words to transfer when the I2C is

configured as a master-transmitter-receiver (MST = 1 and TRX = 1/0 in ICMDR) and the repeat mode is

off (RM = 0 in ICMDR). In the repeat mode (RM = 1), ICCNT is not used.

The value written to ICCNT is copied to an internal data counter. The internal data counter is decremented

by 1 for each data word transferred (ICCNT remains unchanged). If a STOP condition is requested

(STP = 1 in ICMDR), the I2C terminates the transfer with a STOP condition when the countdown is

complete (that is, when the last data word has been transferred).

The data count register (ICCNT) is shown in Figure 18 and described in Table 10.

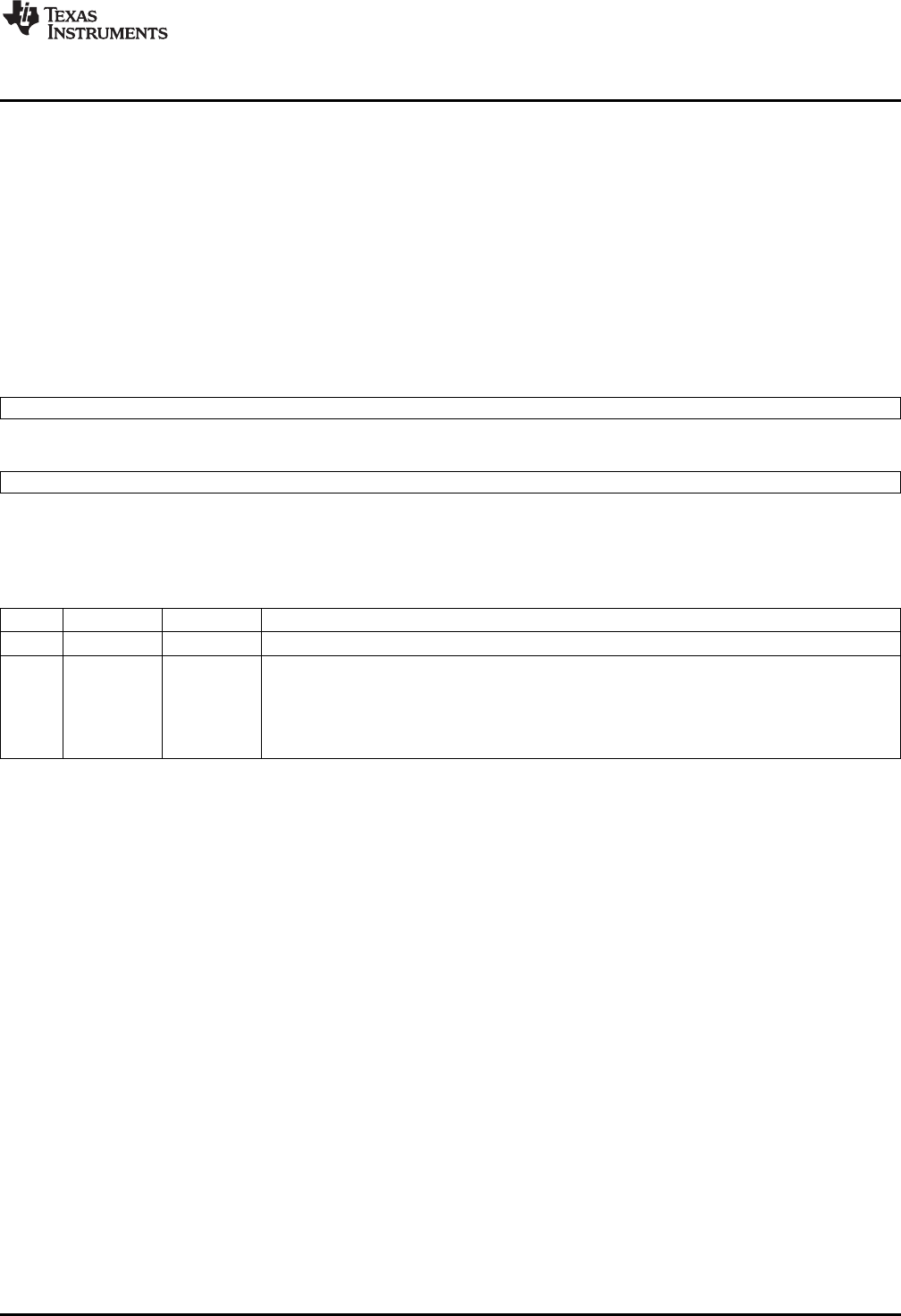

Figure 18. I2C Data Count Register (ICCNT)

31 16

Reserved

R-0

15 0

ICDC

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 10. I2C Data Count Register (ICCNT) Field Descriptions

Bit Field Value Description

31-16 Reserved 0 These reserved bit locations are always read as zeros. A value written to this field has no effect.

15-0 ICDC 0-FFFFh Data count value. When RM = 0 in ICMDR, ICDC indicates the number of data words to transfer in

the nonrepeat mode. When RM = 1 in ICMDR, the value in ICCNT is a don't care. If STP = 1 in

ICMDR, a STOP condition is generated when the internal data counter counts down to 0.

0 The start value loaded to the internal data counter is 65536.

1h-FFFFh The start value loaded to internal data counter is 1-65535.

29

SPRUEN0D–March 2011 Inter-Integrated Circuit (I2C) Peripheral

Submit Documentation Feedback

© 2011, Texas Instruments Incorporated