Registers

www.ti.com

3.4 I2C Clock Divider Registers (ICCLKL and ICCLKH)

When the I2C is a master, the prescaled module clock is divided down for use as the I2C serial clock on

the SCL pin. The shape of the I2C serial clock depends on two divide-down values, ICCL and ICCH. For

detailed information on how these values are programmed, see Section 2.2.

3.4.1 I2C Clock Low-Time Divider Register (ICCLKL)

For each I2C serial clock cycle, ICCL determines the amount of time the signal is low. ICCLKL must be

configured while the I2C is still in reset (IRS = 0 in ICMDR).

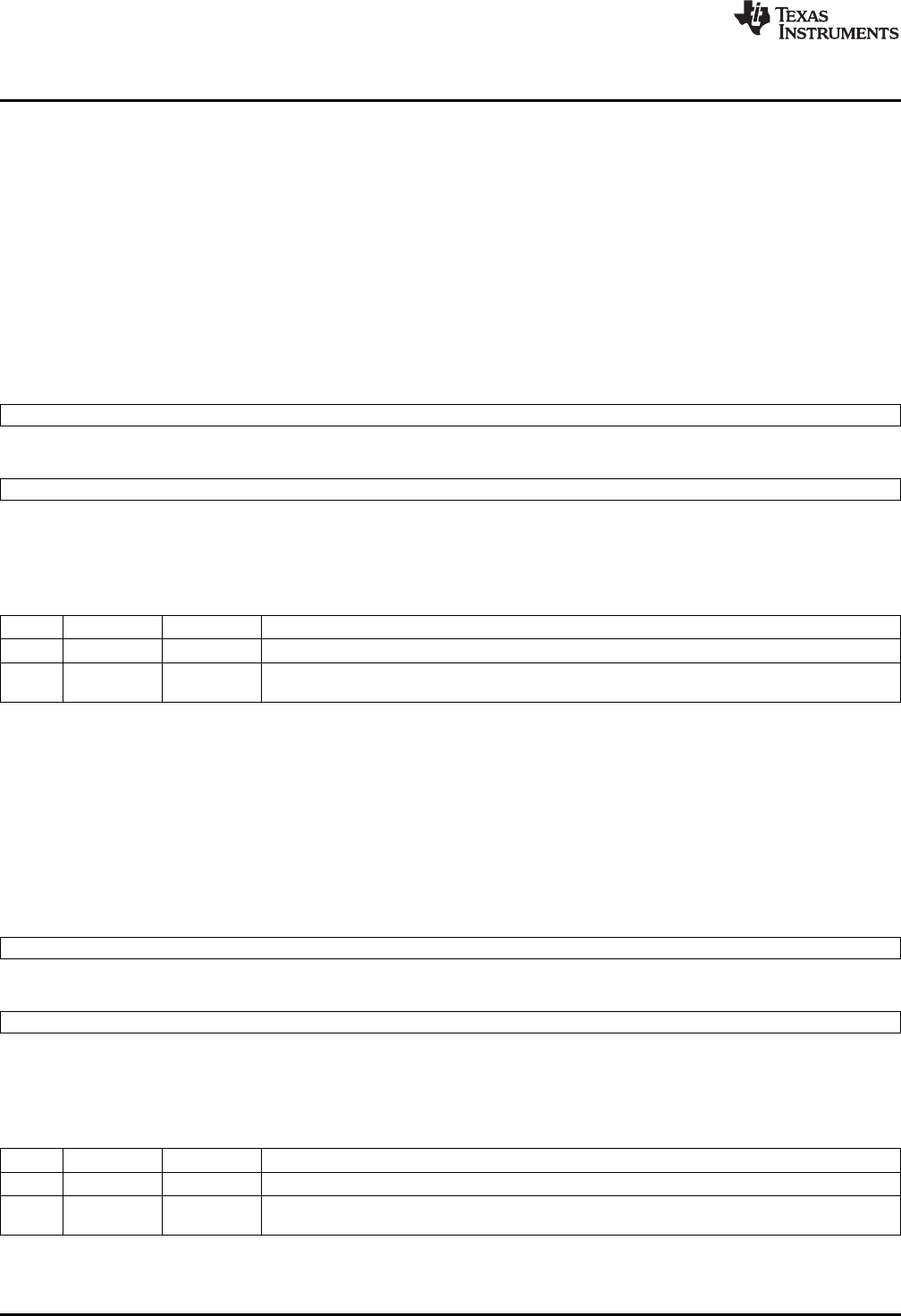

The I2C clock low-time divider register (ICCLKL) is shown in Figure 16 and described in Table 8.

Figure 16. I2C Clock Low-Time Divider Register (ICCLKL)

31 16

Reserved

R-0

15 0

ICCL

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 8. I2C Clock Low-Time Divider Register (ICCLKL) Field Descriptions

Bit Field Value Description

31-16 Reserved 0 These reserved bit locations are always read as zeros. A value written to this field has no effect.

15-0 ICCL 0-FFFFh Clock low-time divide-down value of 1-65536. The period of the module clock is multiplied by

(ICCL + d) to produce the low-time duration of the I2C serial on the SCL pin.

3.4.2 I2C Clock High-Time Divider Register (ICCLKH)

For each I2C serial clock cycle, ICCH determines the amount of time the signal is high. ICCLKH must be

configured while the I2C is still in reset (IRS = 0 in ICMDR).

The I2C clock high-time divider register (ICCLKH) is shown in Figure 17 and described in Table 9.

Figure 17. I2C Clock High-Time Divider Register (ICCLKH)

31 16

Reserved

R-0

15 0

ICCH

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 9. I2C Clock High-Time Divider Register (ICCLKH) Field Descriptions

Bit Field Value Description

31-16 Reserved 0 These reserved bit locations are always read as zeros. A value written to this field has no effect.

15-0 ICCH 0-FFFFh Clock high-time divide-down value of 1-65536. The period of the module clock is multiplied by

(ICCH + d) to produce the high-time duration of the I2C serial on the SCL pin.

28

Inter-Integrated Circuit (I2C) Peripheral SPRUEN0D–March 2011

Submit Documentation Feedback

© 2011, Texas Instruments Incorporated