www.ti.com

Registers

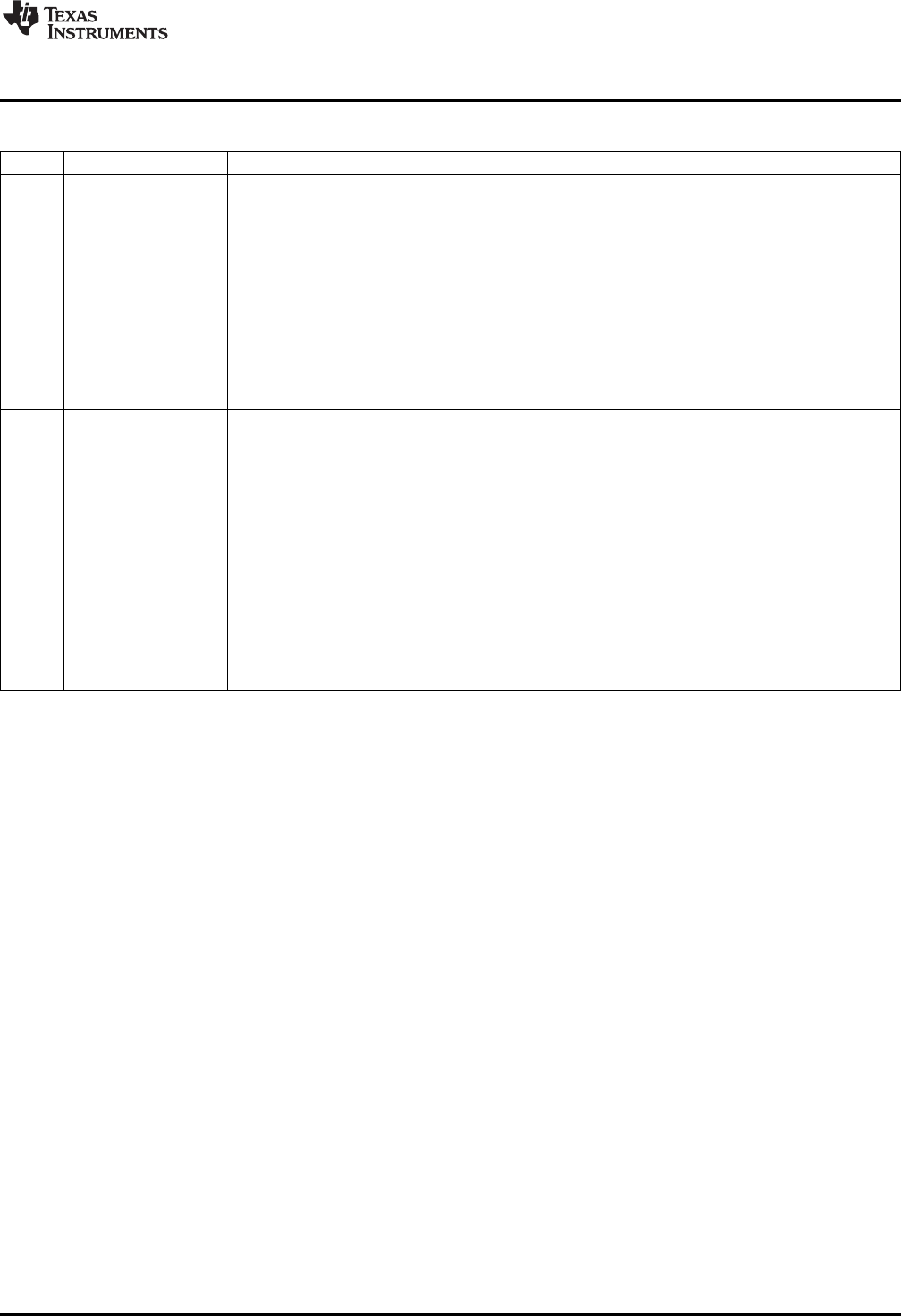

Table 7. I2C Interrupt Status Register (ICSTR) Field Descriptions (continued)

Bit Field Value Description

1 NACK No-acknowledgment interrupt flag bit. NACK applies when the I2C is a transmitter (master or slave).

NACK indicates whether the I2C has detected an acknowledge bit (ACK) or a no-acknowledge bit

(NACK) from the receiver. The CPU can poll NACK or use the NACK interrupt request.

0 ACK received/NACK is not received. NACK is cleared by one of the following events:

• An acknowledge bit (ACK) has been sent by the receiver.

• NACK is manually cleared. To clear this bit, write a 1 to it.

• The CPU reads the interrupt vector register (ICIVR) when the register contains the code for a NACK

interrupt.

• The I2C is reset (either when 0 is written to the IRS bit of ICMDR or when the processor is reset).

1 NACK bit is received. The hardware detects that a no-acknowledge (NACK) bit has been received.

Note: While the I2C performs a general call transfer, NACK is 1, even if one or more slaves send

acknowledgment.

0 AL Arbitration-lost interrupt flag bit (only applicable when the I2C is a master-transmitter). AL primarily

indicates when the I2C has lost an arbitration contest with another master-transmitter. The CPU can poll

AL or use the AL interrupt request.

0 Arbitration is not lost. AL is cleared by one of the following events:

• AL is manually cleared. To clear this bit, write a 1 to it.

• The CPU reads the interrupt vector register (ICIVR) when the register contains the code for an AL

interrupt.

• The I2C is reset (either when 0 is written to the IRS bit of ICMDR or when the processor is reset).

1 Arbitration is lost. AL is set by one of the following events:

• The I2C senses that it has lost an arbitration with two or more competing transmitters that started a

transmission almost simultaneously.

• The I2C attempts to start a transfer while the BB (bus busy) bit is set to 1.

When AL is set to 1, the MST and STP bits of ICMDR are cleared, and the I2C becomes a

slave-receiver.

27

SPRUEN0D–March 2011 Inter-Integrated Circuit (I2C) Peripheral

Submit Documentation Feedback

© 2011, Texas Instruments Incorporated