2

2-13 M32R-FPU Software Manual (Rev.1.01)

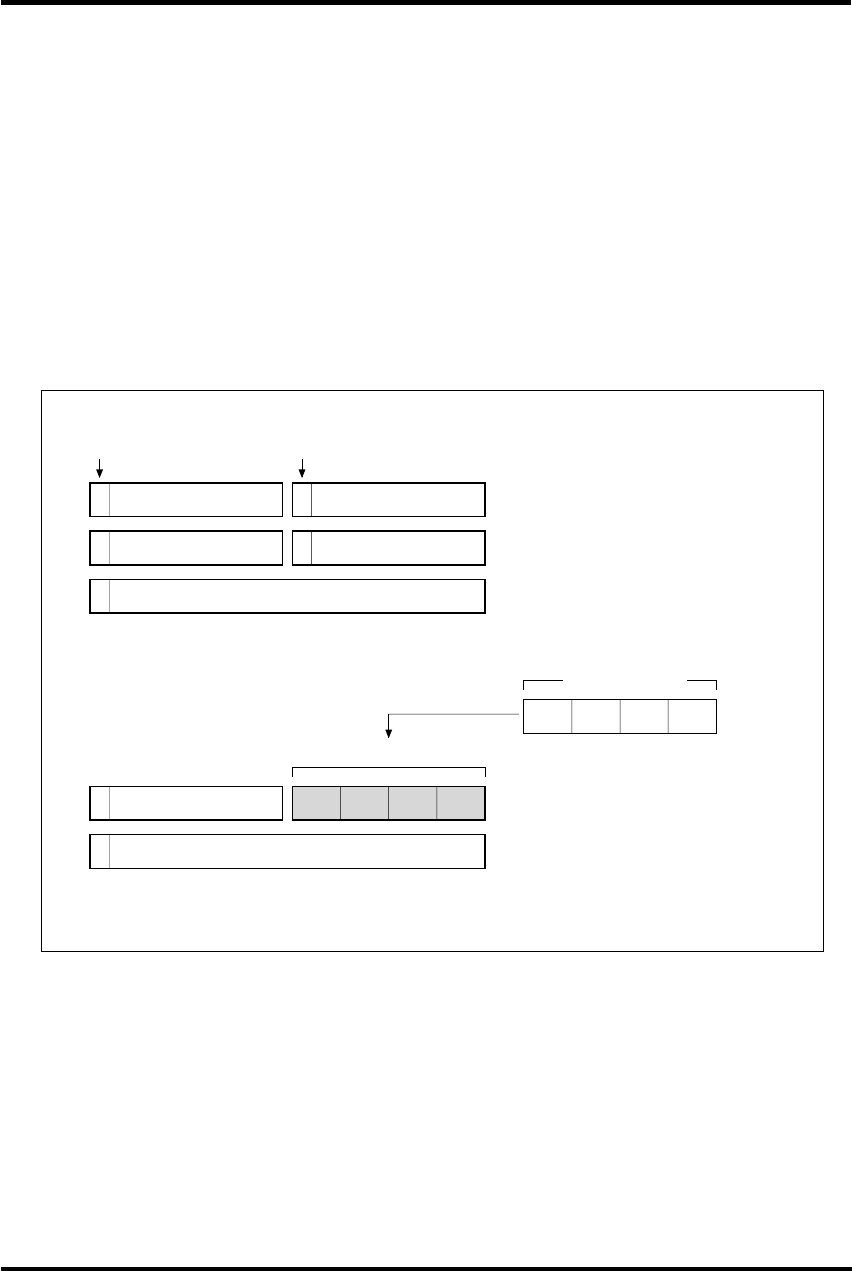

The MSB (Most Significant Bit) of a 32-bit instruction is always "1". The MSB of a 16-bit

instruction in the high-order halfword is always "0" (instruction A in Figure 2.2.3),

however the processing of the following 16-bit instruction depends on the MSB of the

instruction.

In Figure 2.2.3, if the MSB of the instruction B is "0", instructions A and B are executed

sequentially; B is executed after A. If the MSB of the instruction B is "1", instructions A

and B are executed in parallel.

The current implementation allows only the NOP instruction as instruction B for parallel

execution. The MSB of the NOP instruction used for word arraignment adjustment is

changed to "1" automatically by a standard Mitsubishi assembler, then the M32R-FPU

can execute this instruction without requiring any clock cycles.

16-bit instruction A 16-bit instruction B

32-bit instruction

0

16-bit instruction A 16-bit instruction B

01

0

[instruction A] --> [instruction B] sequential

< instruction execution sequence >

MSB

1

1111 0000 0000 0000

16-bit instruction A

0

0111 0000 0000 0000

inserted by assembler

32-bit instruction

1

MSB

NOP instruction whose MSB is changed to "1"

NOP instruction

[instruction A] & [instruction B] parallel

[instruction A] & [NOP] parallel

Fig. 2.2.3 Processing of 16-bit instructions

INSTRUCTION SET

2.2 Instruction format