APPENDICES

APPENDICES-2

M32R-FPU Software Manual (Rev.1.01)

Appendix1 Hexadecimal Instraction Code

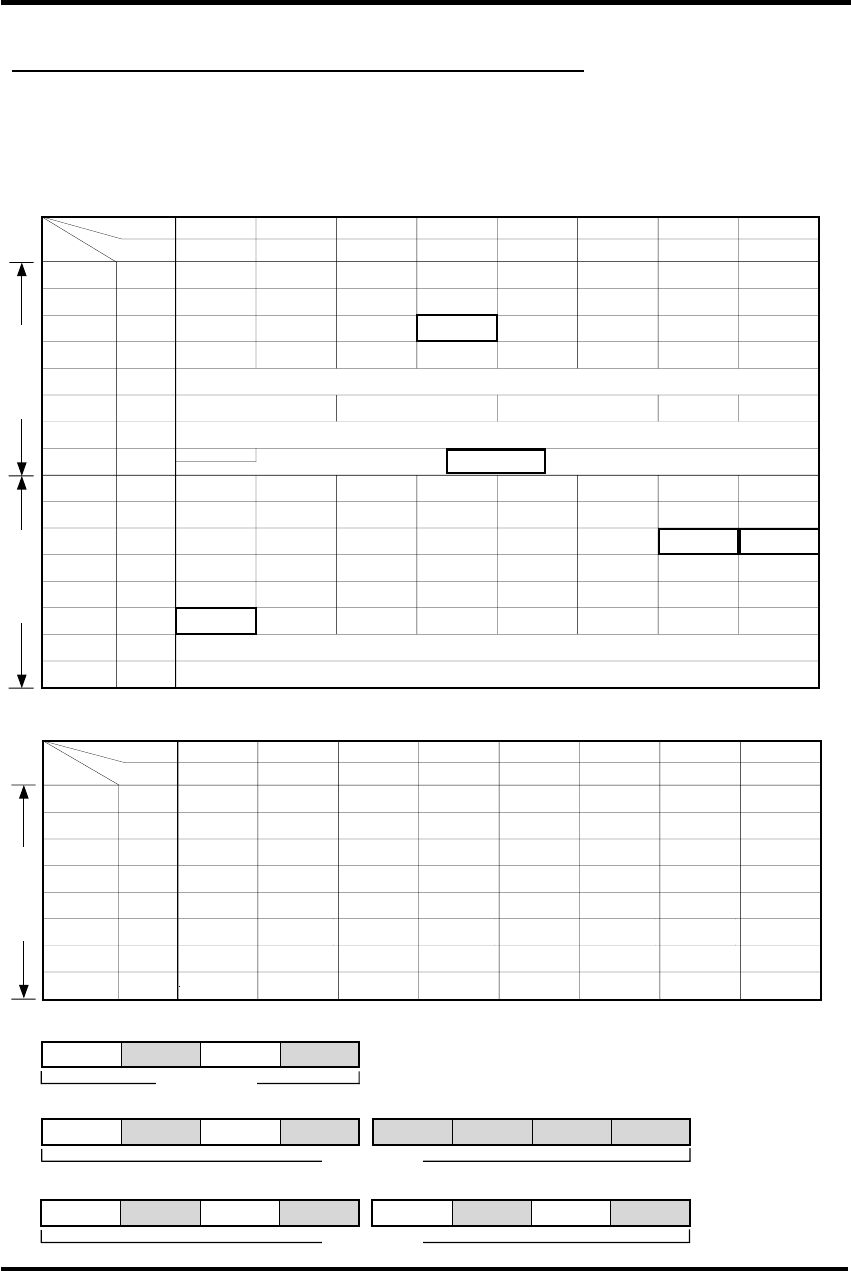

The bit pattern of each instruction and correspondence of mnemonic are shown below.

The instructions enclosed in the bold lines are M32R-FPU extended instructions.

Appendix Table 1.1.1 Instruction Code Table

b0 3 4 7 8 11 12 b15

16-bit instruction

b0-b3 b8-b

11

b0 3 4 7 8 11 12 b15

b0-b3 b8-b11

b16 19 20 23 24 27 28 b31

32-bit instruction

b0 3 4 7 8 11 12 b15

1101 0000 b16-b19 b24-b27

b16 19 20 23 24 27 28 b31

32-bit instruction

b

8

-b

11

b

0

-b

3

0000 0001 0010 0011 0100 0101 0110 0111

01 234567

hexadecimal

numeral

SUBV SUBX SUB

NEG CMP CMPU

Rdest,Rsrc Rdest,Rsrc Rdest,Rsrc Rdest,Rsrc Rsrc1,Rsrc2 Rsrc1,Rsrc2

SRL SRA SLL

MUL

Rdest,Rsrc Rdest,Rsrc Rdest,Rsrc

Rdest,Rsrc

STB STH ST UNLOCK ST ST

Rsrc1,@Rsrc2 Rsrc1,@Rsrc2 Rsrc1,@Rsrc2 Rsrc1,@Rsrc2 Rsrc1,@+Rsrc2 Rsrc1,@-Rsrc2

MULHI MULLO MULWHI MULWLO MACHI MACLO MACWHI MACWLO

Rsrc1,Rsrc2 Rsrc1,Rsrc2 Rsrc1,Rsrc2 Rsrc1,Rsrc2 Rsrc1,Rsrc2 Rsrc1,Rsrc2 Rsrc1,Rsrc2 Rsrc1,Rsrc2

ADDI

Rdest,#imm8

Rdest,#imm5 Rdest,#imm5 Rdest,#imm5

SRLI SRAI SLLI

MVTACHI,

MVTACLO

(

✽

2)

(✽ 1)

CMPI CMPUI

Rsrc,#imm16 Rsrc,#imm16

STB STH ST

Rsrc1,@(disp16,Rsrc2) Rsrc1,@(disp16,Rsrc2) Rsrc1,@(disp16,Rsrc2)

BEQ BNE

Rsrc1,Rsrc2,pcdisp16 Rsrc1,Rsrc2,pcdisp16

LD24

Rdest,#imm24

BC, BNC, BL, BRA

(✽ 1)

16-bit instruction

32-bit instruction

DIVU REM REMUDIV

Rdest,Rsrc Rdest,Rsrc Rdest,RsrcRdest,Rsrc

NOP (✽ 1)

LDI

Rdest,#imm8

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

STH

Rsrc1,@Rsrc2+

BC, BNC, BL, BRA, SETPSW, CLRPSW

BSET

#bitpos,@(disp16,Rsrc)

BCLR

#bitpos,@(disp16,Rsrc)

FPU

externded instruction

APPENDIX 1

Appendix 1 Hexadecimal Instraction Code

b

24

-b

27

b

16

-b

19

hexadecimal

numeral

0000

0001

0010

0011

0100

0101

0110

0111

FADD

FMUL

FDIV

FMADO

ITOF

FSUB

FMSUB

UTOF

0000 0001 0010 0011 0100 0101 0110 0111

0123456

7

32-bit instruction

1

2

3

4

5

6

7

0

FPU extended instruction (b0-b3 = 1101, b8-b11 = 0000)