APPENDICES

APPENDICES-3 M32R-FPU Software Manual (Rev.1.01)

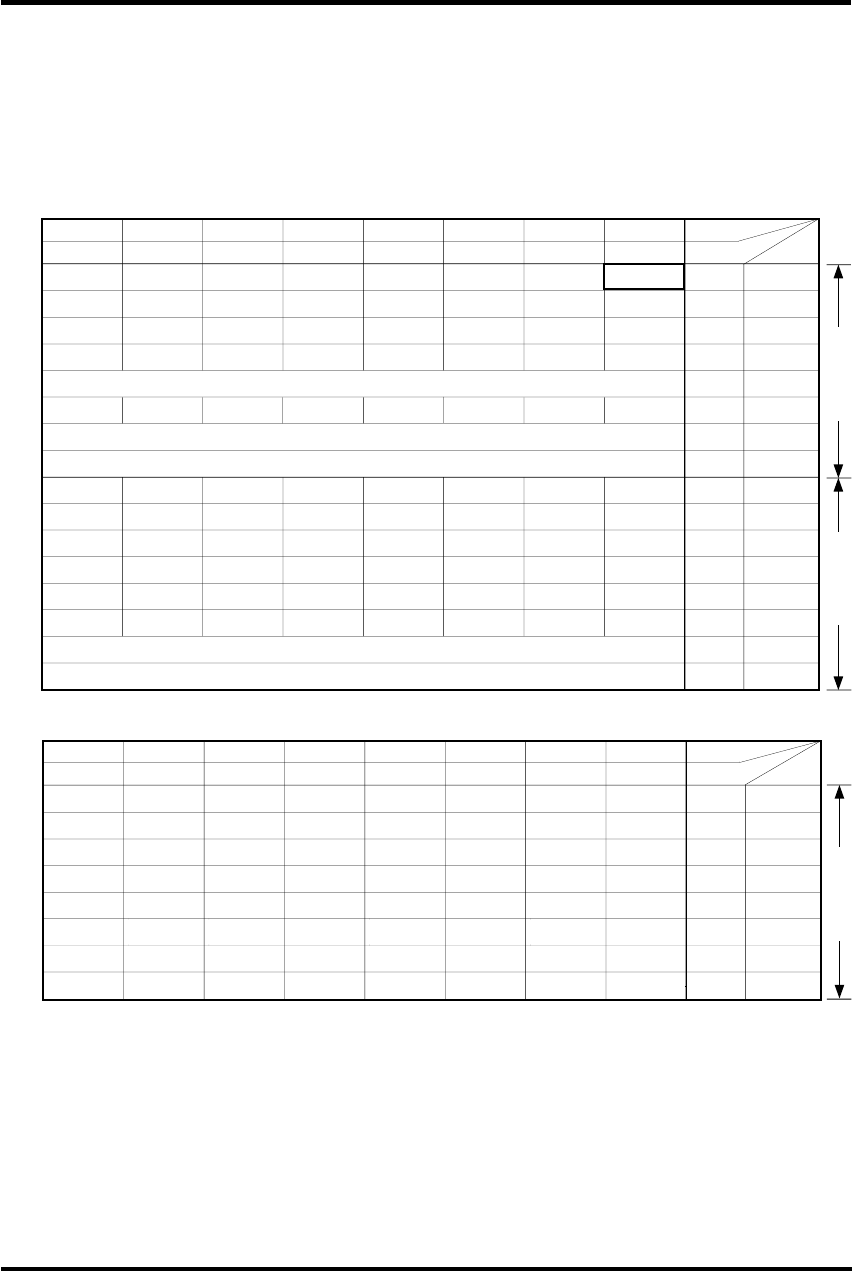

1000 1001 1010 1011 1100

1101 1110

1111

89 BCDEFA

b

8

-b

11

b

0

-b

3

hexadecimal

numeral

16-bit instruction

32-bit instruction

ADDV

Rdest,Rsrc

ADDX

Rdest,Rsrc

ADD

Rdest,Rsrc

NOT

Rdest,Rsrc

AND

Rdest,Rsrc

XOR

Rdest,Rsrc

OR

Rdest,Rsrc

MV

Rdest,Rsrc

MVFC

Rdest,CRsrc

MVTC

Rsrc,CRdest

RTE TRAP

#imm4

JL, JMP

(✽ 1)

LDB

Rdest,@Rsrc

LDUB

Rdest,@Rsrc

LDH

Rdest,@Rsrc

LDUH

Rdest,@Rsrc

LD

Rdest,@Rsrc

LOCK

Rdest,@Rsrc

LD

Rdest,@Rsrc+

ADDI

Rdest,#imm8

RACH RAC

MVFACHI,

MVFACLO,

MVFACMI

(

✽

2)

LDI

Rdest,#imm8

BC, BNC, BL, BRA

(✽ 1)

ADDV3

Rdest,Rsrc,#imm16

ADD3

Rdest,Rsrc,#imm16

AND3

Rdest,Rsrc,#imm16

XOR3

Rdest,Rsrc,#imm16

OR3

Rdest,Rsrc,#imm16

SRL3

Rdest,Rsrc,#imm16

SRA3

Rdest,Rsrc,#imm16

SLL3

Rdest,Rsrc,#imm16

LDI

Rdest,#imm16

LDB

Rdest,@(disp16,Rsrc)

LDUB

Rdest,@(disp16,Rsrc)

LDH

Rdest,@(disp16,Rsrc)

LDUH

Rdest,@(disp16,Rsrc)

LD

Rdest,@(disp16,Rsrc)

BEQZ

Rsrc,pcdisp16

BNEZ

Rsrc,pcdisp16

BLTZ

Rsrc,pcdisp16

BGEZ

Rsrc,pcdisp16

BLEZ

Rsrc,pcdisp16

BGTZ

Rsrc,pcdisp16

SETH

Rdest,#imm16

LD24

Rdest,#imm24

BC, BNC, BL, BRA (✽ 1)

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

BTST

#bitpos,Rsrc

Note. In addition to b0-b3, b8-b11, instructions shown the above ✽1, ✽2 in the table are

decided by the following bit patterns.

As for details of bit patterns of each instruction, refer to "3.2 Instruction description."

✽1: b4-b7, ✽2: b12-b15

APPENDIX 1

Appendix 1 Hexadecimal Instraction Code

b

24

-b

27

b

16

-b

19

32-bit instruction

hexadecimal

numeral

0000

0001

0010

0011

0100

0101

0110

0111

1000 1001 1010 1011 1100 1101 1110 1111

01234567

1

2

3

4

5

6

7

0

FCMPE

FTOI

FCMP

FTOS