APPENDICES

APPENDICES-28

M32R-FPU Software Manual (Rev.1.01)

APPENDIX 6

Appendix 6 M32R-FPU Specification Supplemental Explanation

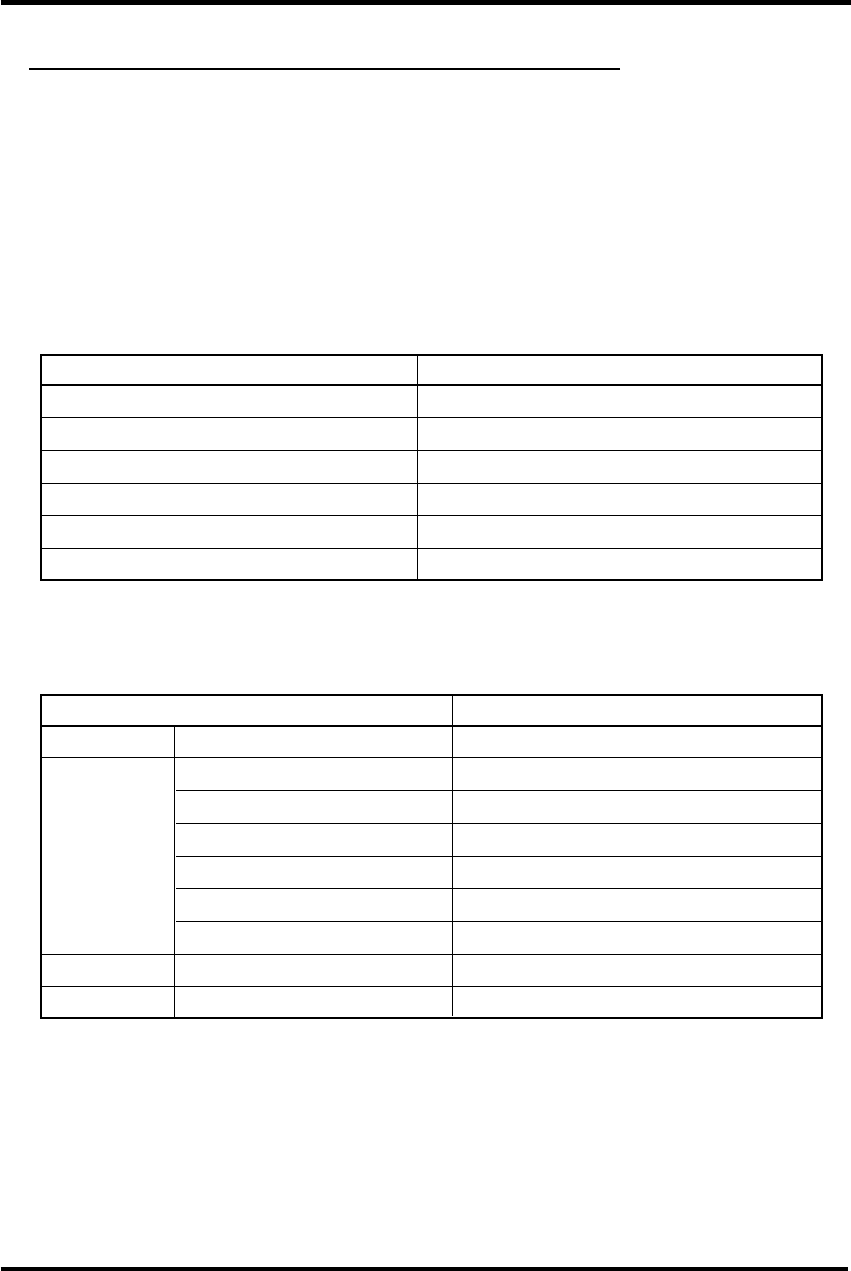

Appendix 6.2 Rules concerning Generation of QNaN in M32R-FPU

The following are rules concerning generating a QNaN as an operation result.

Instructions that generate NaNs as operation results are FADD, FSUB, FMUL, FDIV,

FMADD, and FMSUB.

[Important Note]

This rule does not apply when the data that is sent to Rdest, the results of the FCMP or

FCMPE comparison, comprise a NaN bit pattern.

<FADD, FSUB, FMUL, FDIV>

Source Operand (Rsrc1, Rsrc2) Rdest

SNaN and QNaN SNaN converted to QNaN (Note 1)

Both SNaN Rsrc2 converted to QNaN (Note 1)

Both QNaN Rscr2

SNaN and actual number SNaN converted to QNaN (Note 1)

QNaN and actual number QNaN

Neither operand is NaN; IVLD occurs H'7FFF FFFF

Note 1: SNaN b9 is set to “1” and the operand is converted to QNaN.

<FMADD, FMSUB>

Source Operand Rdest

Rdest Rsrc1, Rsrc2

Actual number SNaN and QNaN SNaN converted to QNaN (Note 1)

Both SNaN Rsrc2 converted to QNaN (Note 1)

Both QNaN Rscr2

SNaN and actual number SNaN converted to QNaN (Note 1)

QNaN and actual number QNaN

Neither operand is NaN; IVLD occurs H'7FFF FFFF

QNaN Don't care Rdest (maintained)

SNaN Don't care Rdest converted to QNaN (Note 1)

Note 1: SNaN b9 is set to “1” and the operand is converted to QNaN.