APPENDICES

APPENDICES-12

M32R-FPU Software Manual (Rev.1.01)

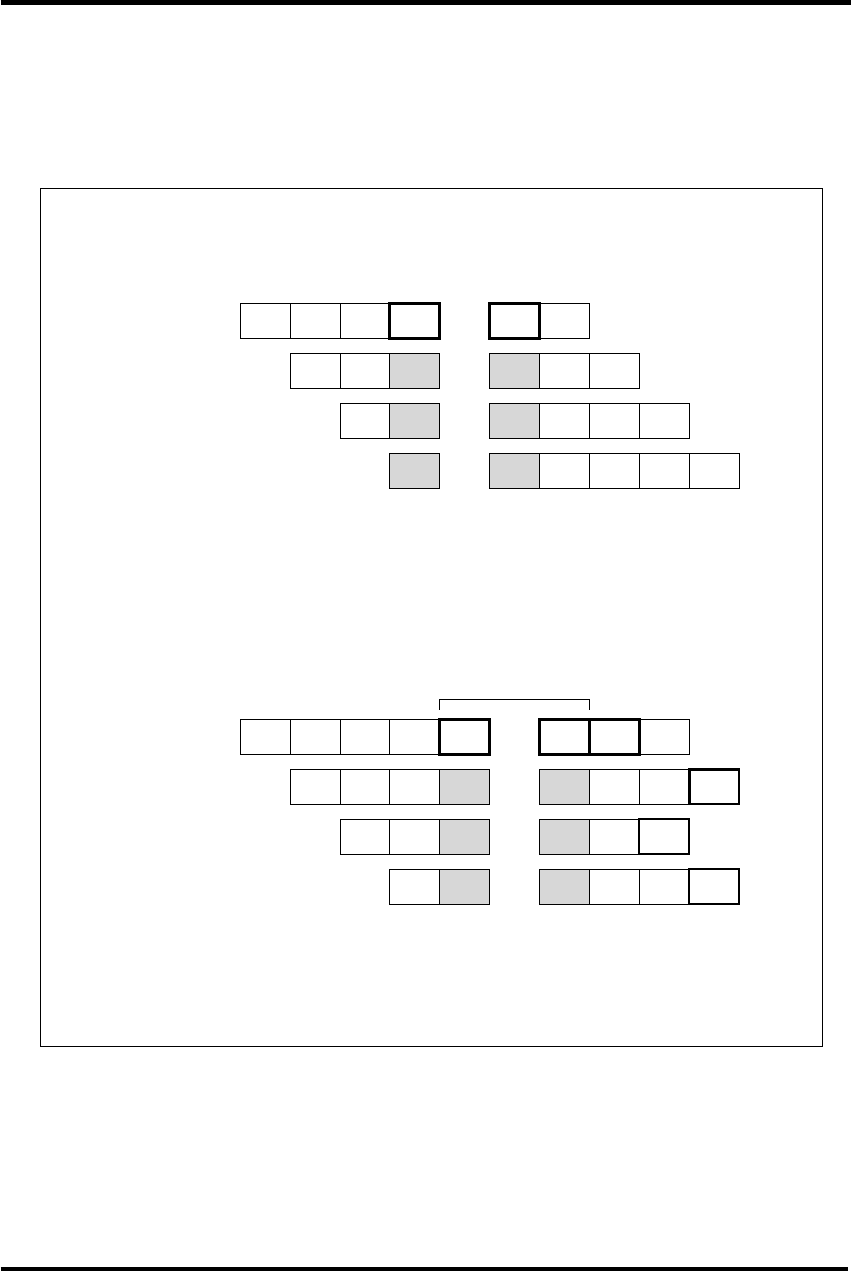

(2) Pipeline Flow with Stalls

A pipeline stage may stall due to execution of a process or branch instruction.

The following diagrams show typical stall cases.

<Case 1> An instruction which requires several cycles is executed in E

IF D E WB

DIV R1,R2

E E

IF D stall WB

ADD R3,R4

Estall

IF D WBEstallstall

IF Dstall WBEstall

ADD R5,R6

ADD R7,R8

<Case 2> An instruction which requires more than 1 cycle for its operand access is executed

IF D E WB

LD R1,@R2

MEM1

IF D WBE stall

IF D stall WBE

IF D WBEstall

ADD R5,R6

ADD R7,R8

MEM1

MEM2MEM1

LD R3,@R4

MEM2MEM1

••••

stall

••••

stall

••••

stall

••••

Other than no-wait

memory access

••••

••••

••••

••••

stall: a pipeline stall

Appendix Figure 3.2.3 Pipeline Flow with Stalls (1)

APPENDIX 3

Appendix 3 Pipeline Processing