1

1-10

M32R-FPU Software Manual (Rev.1.01)

CPU PROGRAMMING MODEL

1.3 Control Registers

(5) Invalid Operation Exception (IVLD)

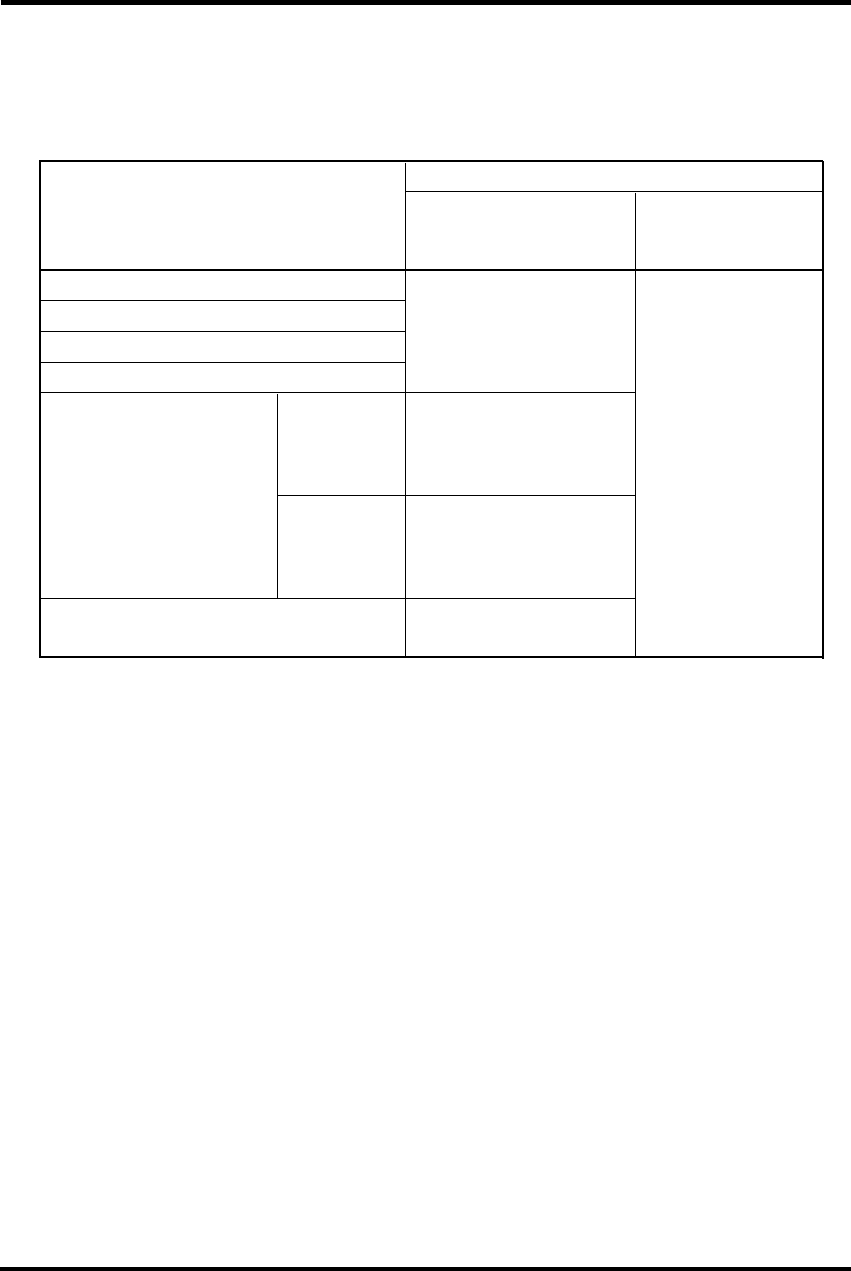

The exception occurs when an invalid operation is executed. The following table shows

the operation results and the respective conditions in which each IVLD occurs.

Occurrence Condition Operation Result (Content of the Destination Register)

When the IVLD EIT processing When the IVLD EIT

is masked (Note 1) processing is executed

(Note 2)

Operation for SNaN operand

+infinity -(+infinity), -infinity -(-infinity) QNaN

0 ✕ infinity

0 ÷ 0, infinity ÷ infinity

When FTOI Return value when

instruction pre-conversion signed bit is:

When an integer conversion was executed "0" = H’7FFF FFFF No change

overflowed "1" = H’8000 0000

When NaN or Infinity was When FTOS Return value when

converted into an integer instruction pre-conversion signed bit is:

was executed "0" = H’0000 7FFF

"1" = H’FFF 8000

When < or > comparison was Comparison results

performed on NaN (comparison invalid)

Note 1: When the Invalid Operation Exception Enable (EV) bit (FPSR register bit 21) = "0"

Note 2: When the Invalid Operation Exception Enable (EV) bit (FPSR register bit 21) = "1"

Notes: • NaN (Not a Number)

SNaN (Signaling NaN): a NaN in which the MSB of the decimal fraction is “0”. When

SNaN is used as the source operand in an operation, an IVLD occurs. SNaNs are useful

in identifying program bugs when used as the initial value in a variable. However,

SNaNs cannot be generated by hardware.

QNaN (Quiet NaN): a NaN in which the MSB of the decimal fraction is "1". Even when

QNaN is used as the source operand in an operation, an IVLD will not occur (excluding

comparison and format conversion). Because a result can be checked by the arithmetic

operations, QNaN allows the user to debug without executing an EIT processing.

QNaNs are created by hardware.

(6) Unimplemented Exception (UIPL)

The exception occurs when the Denormalized Number Zero Flash (DN) bit (FPSR

register bit 23) = "0" and a denormalized number is given as an operation operand

(Note 1).

Because the UIPL has no enable bits available, it cannot be masked when they

occur. The destination register remains unchanged.

Note: • A UDF occurs when the intermediate result of an operation is a denormalized

number, in which case if the DN bit (FPSR register bit 23) = "0", an UIPL occurs.