1

1-6

M32R-FPU Software Manual (Rev.1.01)

CPU PROGRAMMING MODEL

1.3 Control Registers

<At reset release: H0000 0100>

b Bit Name Function R W

0 FS Reflects the logical sum of FU, FZ, FO and FV. R –

Floating-point Exception

Summary Bit

1 FX Set to "1" when an inexact exception occurs R W

Inexact Exception Flag (if EIT processing is unexecuted (Note 1)).

Once set, the flag retains the value "1" until

it is cleared to "0" in software.

2 FU Set to "1" when an underflow exception occurs R W

Underflow Exception Flag (if EIT processing is unexecuted (Note 1)).

Once set, the flag retains the value "1" until

it is cleared to "0" in software.

3 FZ Set to "1" when a zero divide exception occurs R W

Zero Divide Exception Flag (if EIT processing is unexecuted (Note 1)).

Once set, the flag retains the value "1" until

it is cleared to "0" in software.

4 FO Set to "1" when an overflow exception occurs R W

Overflow Exception Flag (if EIT processing is unexecuted (Note 1)).

Once set, the flag retains the value "1" until

it is cleared to "0" in software.

5 FV Set to "1" when an invalid operation exception R W

Invalid Operation Exception occurs (if EIT processing is unexecuted (Note 1)).

Flag Once set, the flag retains the value "1" until

it is cleared to "0" in software.

6–16 No function assigned. Fix to "0". 0 0

17 EX 0: Mask EIT processing to be executed when an R W

Inexact Exception Enable inexact exception occurs

Bit 1: Execute EIT processing when an inexact

exception occurs

18 EU 0: Mask EIT processing to be executed when an R W

Underflow Exception Enable underflow exception occurs

Bit 1: Execute EIT processing when an underflow

exception occurs

19 EZ 0: Mask EIT processing to be executed when a R W

Zero Divide Exception zero divide exception occurs

Enable Bit 1: Execute EIT processing when a zero divide

exception occurs

20 EO 0: Mask EIT processing to be executed when an R W

Overflow Exception overflow exception occurs

Enable Bit 1: Execute EIT processing when an overflow

exception occurs

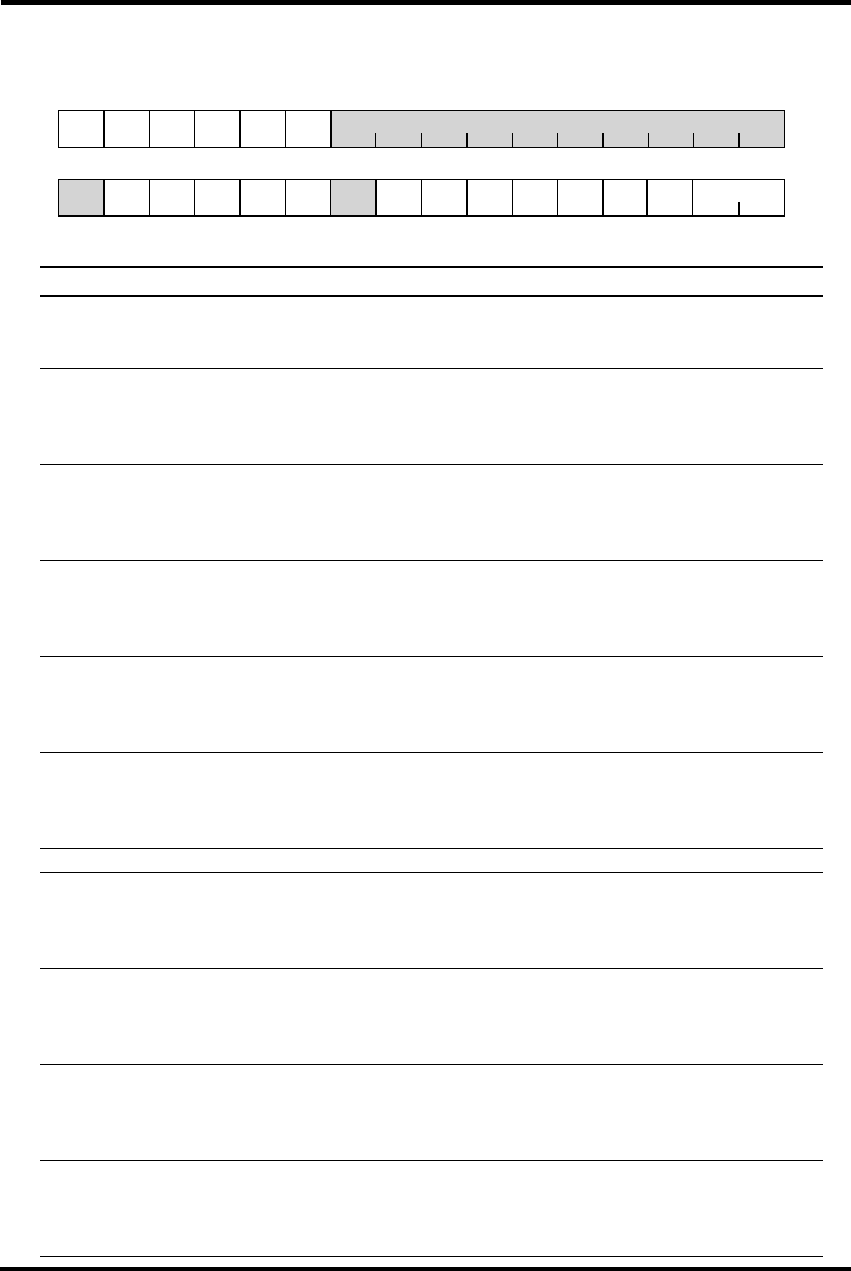

1.3.5 Floating-point Status Register: FPSR (CR7)

0000 00 0 0000000

234567891011121314b151b0

00 00000100000000

EV

DN CE CX CU CZ CO CV RM

18 19 20 21 22 23 24 25 26 27 28 29 30 b3117b16

EUEX

FS FX FU FZ

0

FO

0

FV

EZ EO