APPENDICES

APPENDICES-27 M32R-FPU Software Manual (Rev.1.01)

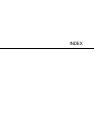

(4) When Inexact Operation Exception occurs in Step 1

■ If an Inexact Operation occurs due to rounding:

<When EX = 0: IXCT occurs>

Type of R0 Condition FMUL + FADD Operation FMADD Operation

Normalized – R0 = rounded value of Same as left

number, 0, R1*R2 + R0

Infinity

Denormalized DN=0 UIPL occurs, EIT occurs Same as left

number R0 = maintained

DN=1 R0 = rounded value of Same as left

R1*R2

QNaN – R0 = maintained (QNaN) Same as left

SNaN EV=0 IVLD occurs Same as left

R0 = R0 converted to QNaN

EV=1 IVLD occurs, EIT occurs Same as left

R0 = maintained (SNaN)

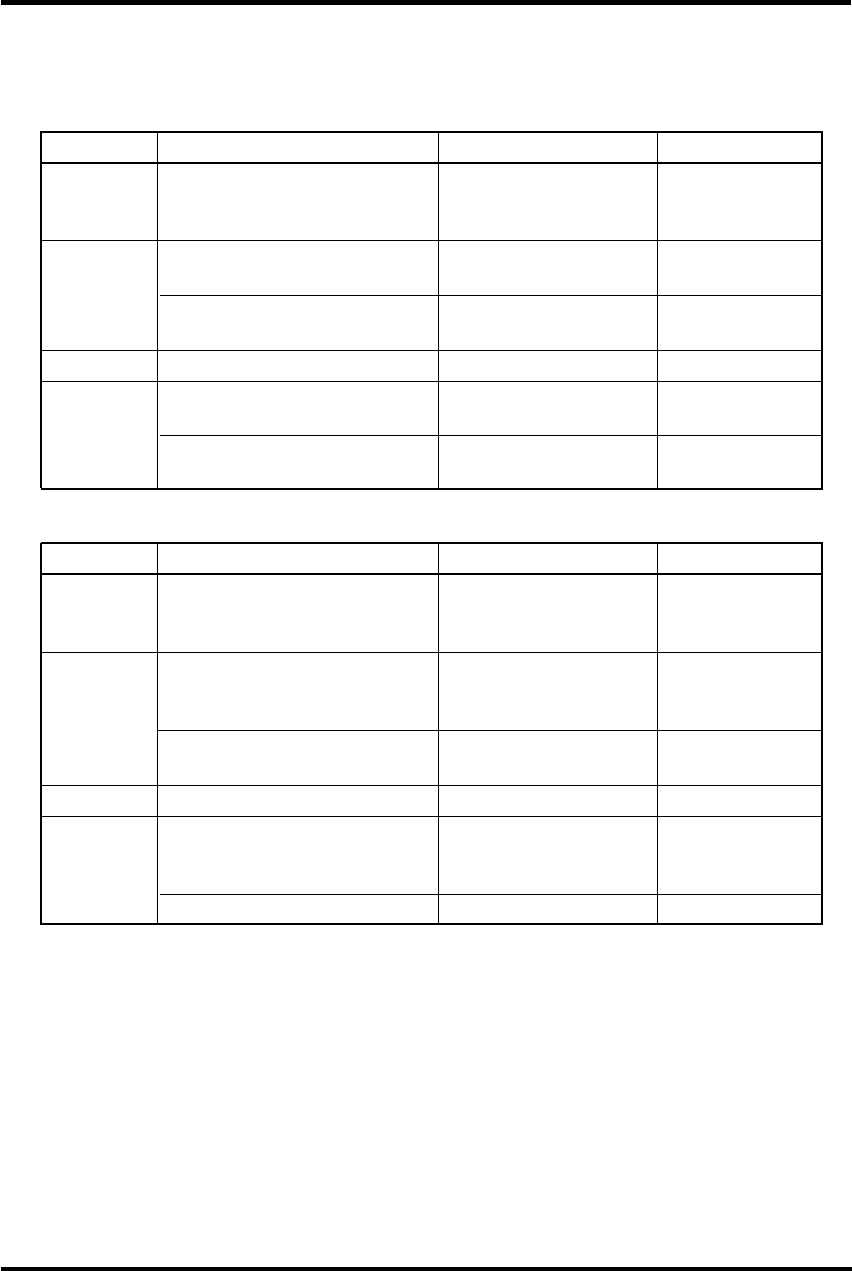

<When EX = 1: IXCT occurs>

Type of R0 Condition FMUL + FADD Operation FMADD Operation

Normalized – EIT occurs when FMUL is EIT occurs,

number, 0, completed R0 = maintained

Infinity R0 = maintained

Denormalized DN=0 Same as above UIPL occurs,

number EIT occurs

R0 = maintained

DN=0 Same as above EIT occurs

R0 = maintained

QNaN – Same as above Same as above

SNaN EV=0 Same as above IVLD occurs,

EIT occurs

R0 = maintained

EV=1 Same as above Same as above

■ When an Inexact Operation occurs due to an OVF at EO = 0:

<When EV = 0: IXCT occurs>

Refer to “(1) Overflow occurs in Step 1 <When EO = 0, EX = 0: OVF and IXCT occur>”.

<When EV = 1: IXCT occurs>

Same results as “■ If an Inexact Operation occurs due to rounding <when EX = 1: IXCT

occurs>”.

APPENDIX 6

Appendix 6 M32R-FPU Specification Supplemental Explanation