6−2

Table 6−1 lists the definitions used by the I

2

C protocol.

Table 6−1. I

2

C Protocol Definitions

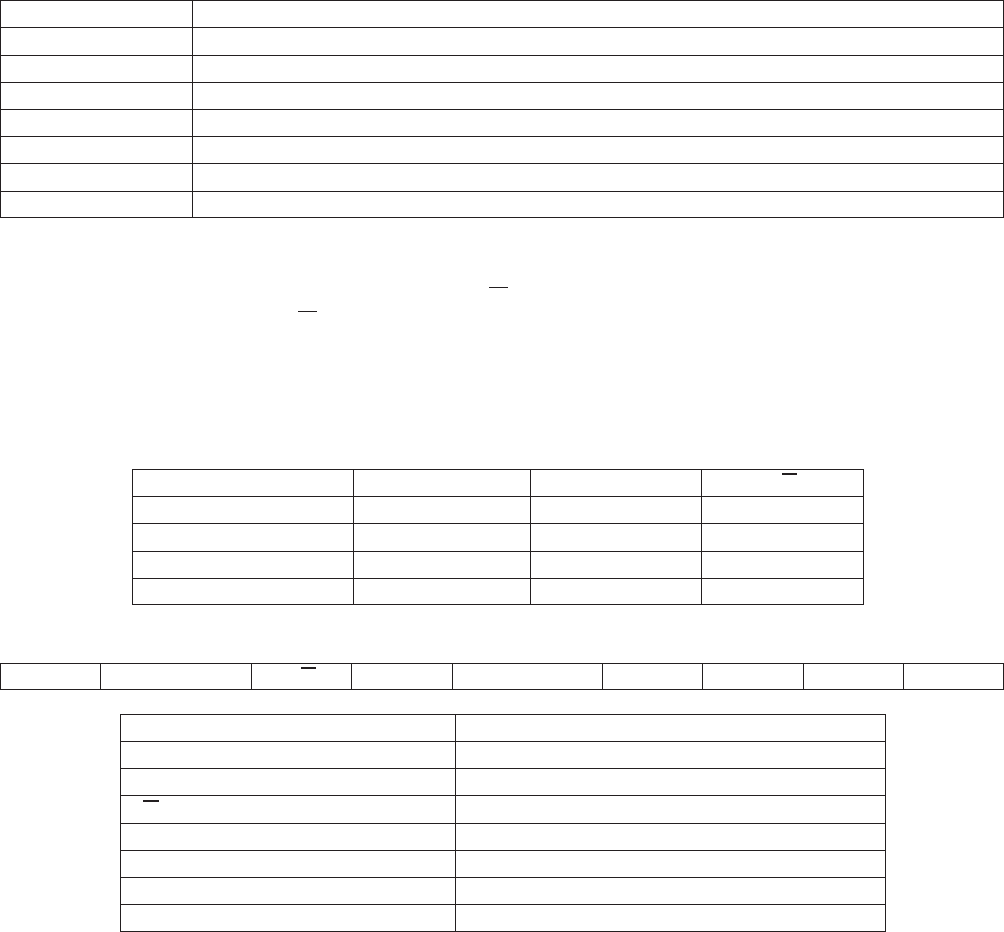

DEFINITION DESCRIPTION

Transmitter The device that sends data

Receiver The device that receives data

Master The device that initiates a transfer, generates clock signals, and terminates the transfer

Slave The device addressed by the master

Multimaster More than one master can attempt to control the bus at the same time without corrupting the message.

Arbitration Procedure to ensure the message is not corrupted when two masters attempt to control the bus.

Synchronization Procedure to synchronize the clock signals of two or more devices

6.3 Operation

The 7-bit address for the TAS3002 device is 0110 10X R/W where X is a programmable address bit, set by terminal 7

(CS1). Combining CS1 and the R/W

bit, the TAS3002 device can respond to four different I

2

C addresses (two read

and two write). These two addresses are licensed I

2

C addresses that do not conflict with other licensed I

2

C audio

devices. In addition to the 7-bit device address, subaddresses direct communication to the proper memory location

within the device. A complete table of subaddresses and control registers is provided in Appendix A. For example,

to change bass to 10-dB gain, Section 6.3.1 shows the data that is written to the I

2

C port:

Table 6−2. I

2

C Address Byte Table

I

2

C ADDRESS BYTE A6−A1 CS1 (A0) R/W

68h 011010 0 0

69h 011010 0 1

6Ah 011010 1 0

6Bh 011010 1 1

6.3.1 Write Cycle Example

Start Slave Address R/W A Subaddress A Data A Stop

FUNCTION DESCRIPTION

Start Start condition as defined in I

2

C

Slave address 0110100 (CS1 = 0)

R/W 0 (write)

A Acknowledgement as defined in I

2

C (slave)

Subaddress (treble control register) 0000 0101

Data (0 dB gain) 0111 0010

Stop Stop condition as defined in I

2

C

NOTE: Table is for serial data (SDA); serial clock (SCL) is not shown but conditions apply as well.

Whenever writing to a subaddress, the correct number of data bytes must follow in order to complete the write cycle.

For example, if the volume control register with subaddress 04h is written to, six bytes of data must follow; otherwise,

the cycle is incomplete and errors occur.