2−5

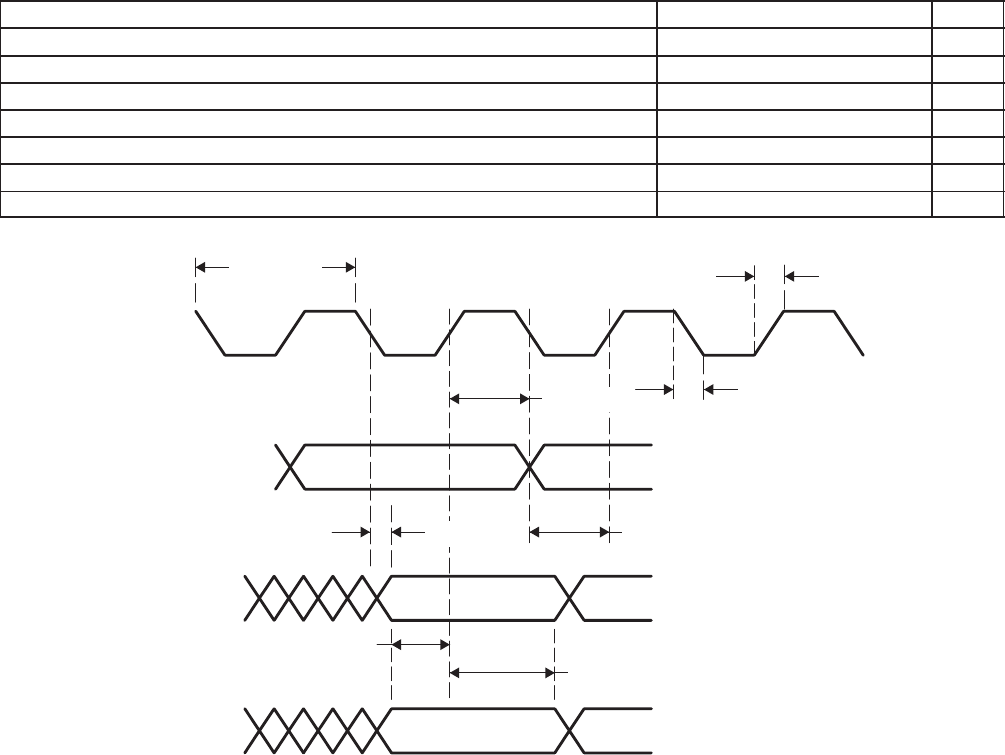

2.3 Switching Characteristics

PARAMETER MIN TYP MAX UNIT

t

c(SCLK)

SCLK cycle time 325.5 ns

t

d(SLR)

SCLK rising to LRCLK edge 20 ns

t

d(SDOUT)

SDOUT valid from SCLK falling edge (see Note 1) (1/256f

S

) + 10 ns

t

su(SDIN)

SDIN setup before SCLK rising edge 20 ns

t

h(SDIN)

SDIN hold after SCLK rising edge 100 ns

f

(LRCLK)

LRCLK frequency 32 44.1 48 kHz

Duty cycle 50 %

NOTE 1: Maximum of 50-pF external load on SDOUT.

SCLK

LRCLK

SDIN1

SDIN2

SDOUT1

SDOUT2

SDOUT0

t

c(SCLK)

t

d(SDOUT)

t

su(SDIN)

t

h(SDIN)

t

d(SLR)

t

f(SCLK)

t

r(SCLK)

t

d(SLR)

Figure 2−4. For Right-/Left-Justified and I

2

S Serial Protocols