CHAPTER 3 - BIOS SETUP

SYS7180VE User’s Manual

35

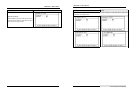

Description Choice

CAS Latency Time

When synchronous DRAM is installed, the

number of clock cycles of CAS latency depends

on the DRAM timing. Do not reset this field

from the default value specified by the system

designer.

You can select CAS latency time in HCLK of

2/2 or 3/3. The system board designer should set

the values in this field, depends on the DRAM

installed specifications of the installed DRAM

or the installed CPU.

Active to Precharge delay

Select the precharge delay timer.

DRAM RAS# to CAS# delay

This field lets you insert a timing delay between

the CAS and RAS strobe signals, used when

DRAM is written to, read from, or refreshed.

Fast gives faster performance; and Slow gives

more stable performance. This field applies only

when synchronous DRAM is installed in the

system.

DRAM RAS# Precharge

The precharge time is the number of cycles it

takes for the RAS to accumulate its charge

b

efore DRAM refresh. If insufficient time is

allowed, refresh may be incomplete and the

DRAM may fail to retain data.

CHAPTER 3 - BIOS SETUP

36

SYS7180VE User’s Manual

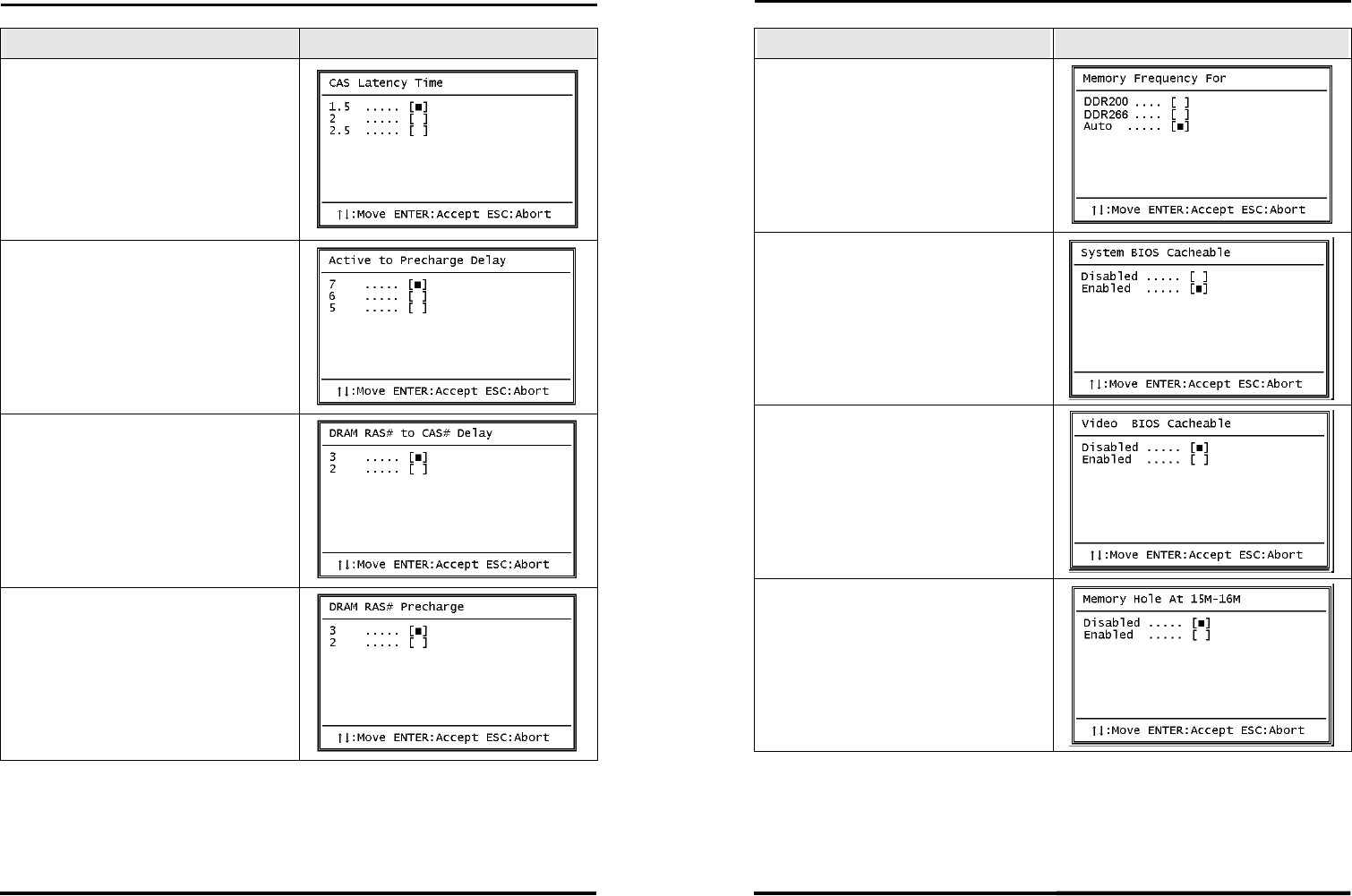

Description Choice

Memory Frequency for

Select the memory frequency for

DDR200/DDR266 when install the memory with

specification of DDR200, or when install the

memory with specification of DDR266, or Auto

define by the BIOS.

System BIOS Cacheable

Selecting Enabled allows caching of the system

BIOS ROM at F0000h-FFFFFh, resulting in

b

etter system performance. However, if any

program writes to this memory area, a system

error may result.

Video BIOS Cacheable

Selecting Enabled allows caching of the video

BIOS ROM at C0000h to C7FFFh, resulting in

b

etter video performance. However, if any

program writes to this memory area, a system

error may result.

Memory Hole At 15M-16M

You can reserve this area of system memory for

ISA adapter ROM. When this area is reserved, it

cannot be cached. The user information of

peripherals that need to use this area of system

memory usually discusses their memory

requirements.