INT1

to

INT12

INT14

C28x

TINT2

TINT0

PIE

CPU-TIMER0

CPU-TIMER2

(Reservedfor

DSP/BIOS)

INT13

TINT1

CPU-TIMER1

XINT13

TMS320F2809, TMS320F2808, TMS320F2806

TMS320F2802, TMS320F2801, TMS320C2802

TMS320C2801, TMS320F28016, TMS320F28015

SPRS230L–OCTOBER 2003–REVISED DECEMBER 2009

www.ti.com

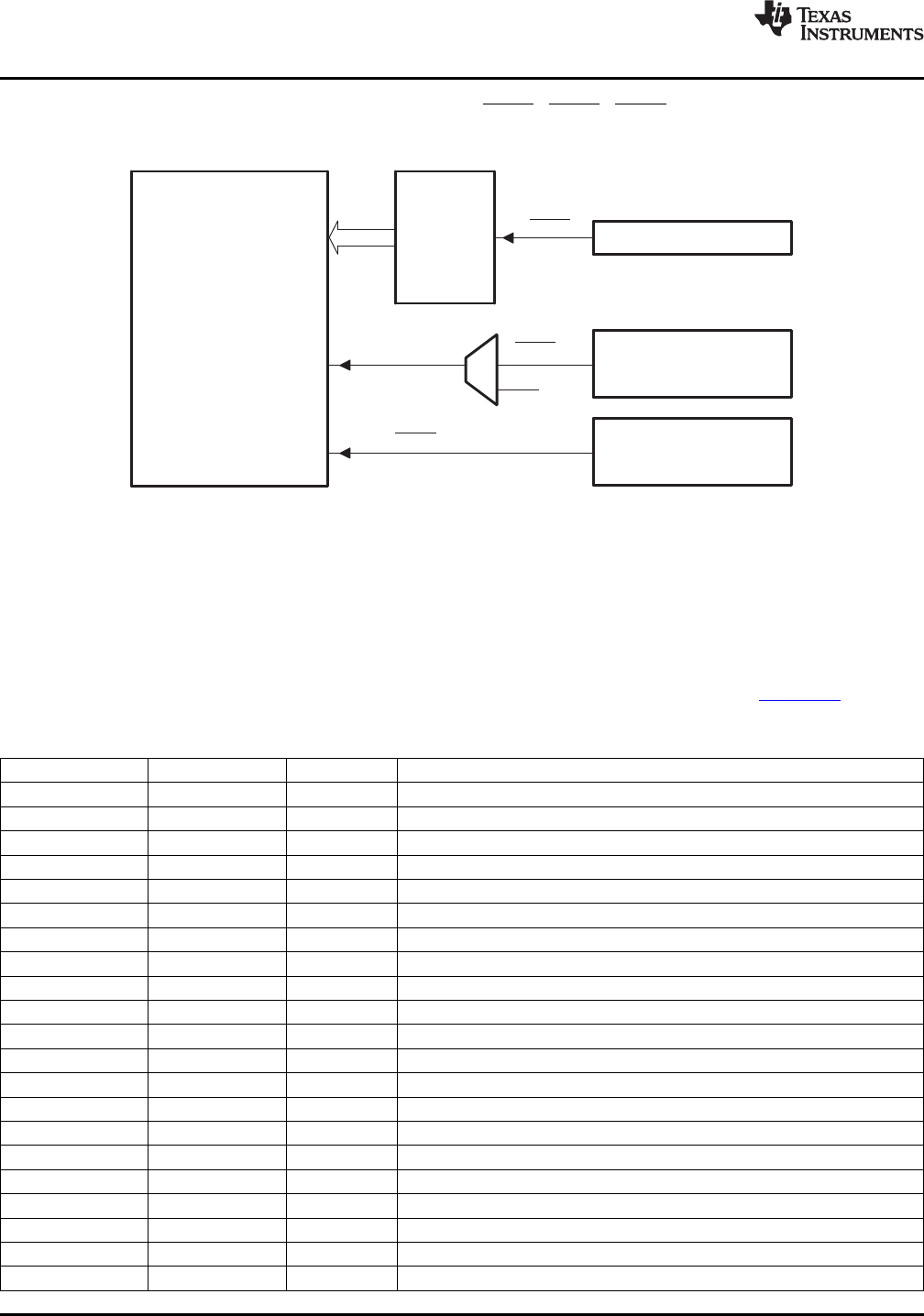

In the 280x devices, the timer interrupt signals (TINT0, TINT1, TINT2) are connected as shown in

Figure 4-2.

A. The timer registers are connected to the memory bus of the C28x processor.

B. The timing of the timers is synchronized to SYSCLKOUT of the processor clock.

Figure 4-2. CPU-Timer Interrupt Signals and Output Signal

The general operation of the timer is as follows: The 32-bit counter register "TIMH:TIM" is loaded with the

value in the period register "PRDH:PRD". The counter register decrements at the SYSCLKOUT rate of the

C28x. When the counter reaches 0, a timer interrupt output signal generates an interrupt pulse. The

registers listed in Table 4-1 are used to configure the timers. For more information, see the TMS320x280x,

2801x, 2804x DSP System Control and Interrupts Reference Guide (literature number SPRU712).

Table 4-1. CPU-Timers 0, 1, 2 Configuration and Control Registers

NAME ADDRESS SIZE (x16) DESCRIPTION

TIMER0TIM 0x0C00 1 CPU-Timer 0, Counter Register

TIMER0TIMH 0x0C01 1 CPU-Timer 0, Counter Register High

TIMER0PRD 0x0C02 1 CPU-Timer 0, Period Register

TIMER0PRDH 0x0C03 1 CPU-Timer 0, Period Register High

TIMER0TCR 0x0C04 1 CPU-Timer 0, Control Register

Reserved 0x0C05 1 Reserved

TIMER0TPR 0x0C06 1 CPU-Timer 0, Prescale Register

TIMER0TPRH 0x0C07 1 CPU-Timer 0, Prescale Register High

TIMER1TIM 0x0C08 1 CPU-Timer 1, Counter Register

TIMER1TIMH 0x0C09 1 CPU-Timer 1, Counter Register High

TIMER1PRD 0x0C0A 1 CPU-Timer 1, Period Register

TIMER1PRDH 0x0C0B 1 CPU-Timer 1, Period Register High

TIMER1TCR 0x0C0C 1 CPU-Timer 1, Control Register

Reserved 0x0C0D 1 Reserved

TIMER1TPR 0x0C0E 1 CPU-Timer 1, Prescale Register

TIMER1TPRH 0x0C0F 1 CPU-Timer 1, Prescale Register High

TIMER2TIM 0x0C10 1 CPU-Timer 2, Counter Register

TIMER2TIMH 0x0C11 1 CPU-Timer 2, Counter Register High

TIMER2PRD 0x0C12 1 CPU-Timer 2, Period Register

TIMER2PRDH 0x0C13 1 CPU-Timer 2, Period Register High

TIMER2TCR 0x0C14 1 CPU-Timer 2, Control Register

54 Peripherals Copyright © 2003–2009, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320F2809 TMS320F2808 TMS320F2806 TMS320F2802 TMS320F2801 TMS320C2802

TMS320C2801 TMS320F28016 TMS320F28015