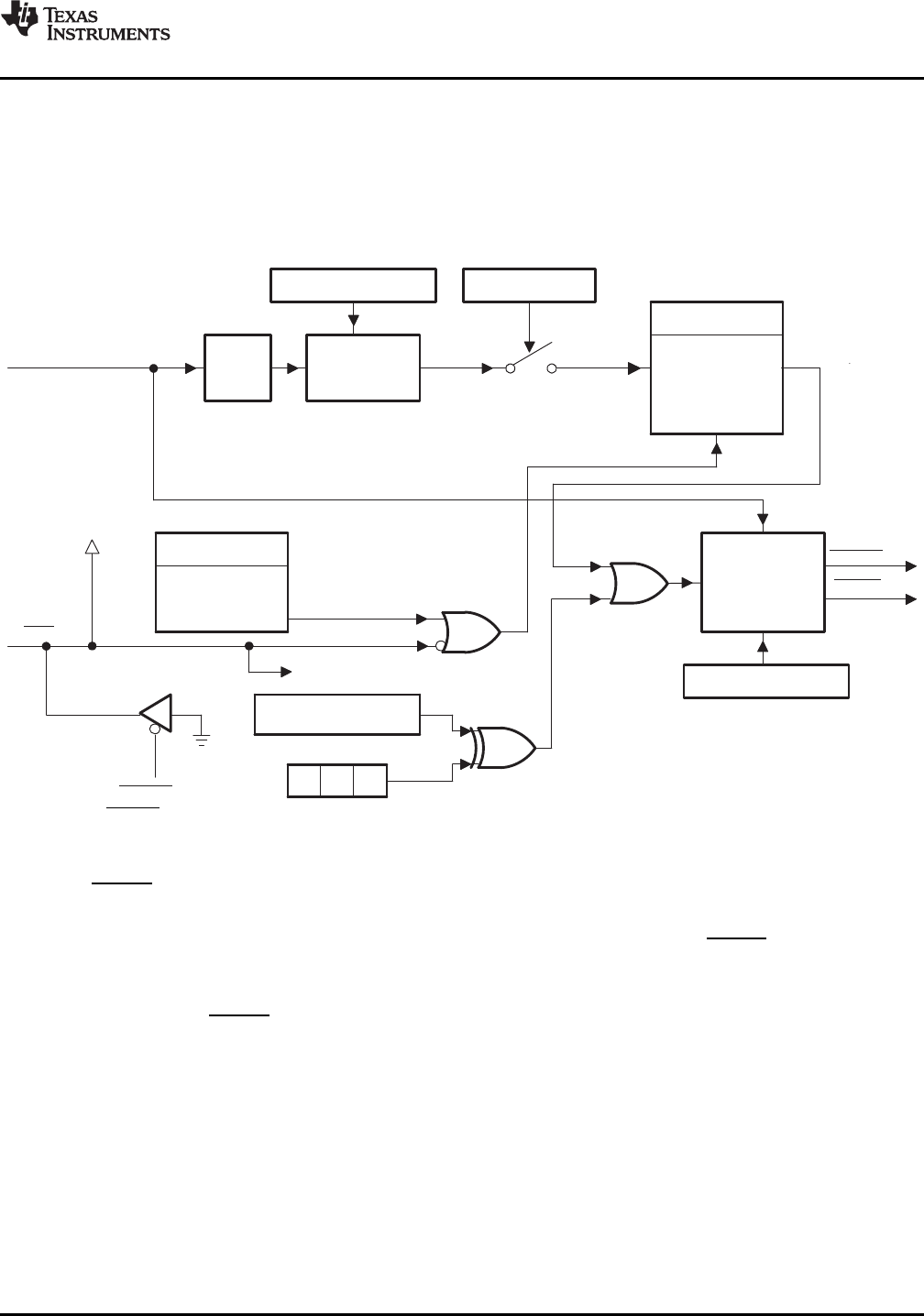

/512

OSCCLK

WDCR (WDPS(2:0))

WDCLK

WDCNTR(7:0)

WDKEY(7:0)

Good Key

1 0 1

WDCR (WDCHK(2:0))

Bad

WDCHK

Key

WDCR (WDDIS)

Clear Counter

SCSR (WDENINT)

Watchdog

Prescaler

Generate

Output Pulse

(512 OSCCLKs)

8-Bit

Watchdog

Counter

CLR

WDRST

WDINT

Watchdog

55 + AA

Key Detector

XRS

Core-reset

WDRST

(A)

Internal

Pullup

TMS320F2809, TMS320F2808, TMS320F2806

TMS320F2802, TMS320F2801, TMS320C2802

TMS320C2801, TMS320F28016, TMS320F28015

www.ti.com

SPRS230L–OCTOBER 2003–REVISED DECEMBER 2009

3.6.2 Watchdog Block

The watchdog block on the 280x is similar to the one used on the 240x and 281x devices. The watchdog

module generates an output pulse, 512 oscillator clocks wide (OSCCLK), whenever the 8-bit watchdog up

counter has reached its maximum value. To prevent this, the user disables the counter or the software

must periodically write a 0x55 + 0xAA sequence into the watchdog key register which will reset the

watchdog counter. Figure 3-14 shows the various functional blocks within the watchdog module.

A. The WDRST signal is driven low for 512 OSCCLK cycles.

Figure 3-14. Watchdog Module

The WDINT signal enables the watchdog to be used as a wakeup from IDLE/STANDBY mode.

In STANDBY mode, all peripherals are turned off on the device. The only peripheral that remains

functional is the watchdog. The WATCHDOG module will run off OSCCLK. The WDINT signal is fed to the

LPM block so that it can wake the device from STANDBY (if enabled). See Section 3.7, Low-Power

Modes Block, for more details.

In IDLE mode, the WDINT signal can generate an interrupt to the CPU, via the PIE, to take the CPU out of

IDLE mode.

In HALT mode, this feature cannot be used because the oscillator (and PLL) are turned off and hence so

is the WATCHDOG.

Copyright © 2003–2009, Texas Instruments Incorporated Functional Overview 51

Submit Documentation Feedback

Product Folder Link(s): TMS320F2809 TMS320F2808 TMS320F2806 TMS320F2802 TMS320F2801 TMS320C2802

TMS320C2801 TMS320F28016 TMS320F28015