50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

GPIO0/EPWM1A

TCK

TMS

TDI

GPIO23/EQEP1I/SPISTEC/SCIRXDB

GPIO22/EQEP1S/SPICLKC/SCITXDB

GPIO11/EPWM6B/SCIRXDB/ECAP4

GPIO21/EQEP1B/SPISOMIC/CANRXB

XCLKOUT

GPIO20/EQEP1A/SPISIMOC/CANTXB

GPIO9/EPWM5B/SCITXDB/ECAP3

GPIO7/EPWM4B/SPISTED/ECAP2

GPIO19/SPISTEA/SCIRXDB

GPIO6/EPWM4A/EPWMSYNCI/EPWMSYNCO

GPIO18/SPICLKA/SCITXDB

GPIO5/EPWM3B/SPICLKD/ECAP1

GPIO4/EPWM3A

XRS

TRST

V

SS

V

DD

V

DDIO

GPIO10/EPWM6A/CANRXB/ADCSOCBO

V

SS

GPIO8/EPWM5A/CANTXB/ADCSOCAO

V

DD

V

SS

GPIO17/SPISOMIA/CANRXB/TZ6

V

SS

V

SS

V

DD

V

DDIO

GPIO16/SPISIMOA/CANTXB/TZ5

V

DD2A18

V

SS2AGND

V

DDAIO

GPIO12/TZ1/CANTXB/SPISIMOB

V

SS

V

DDIO

GPIO29/SCITXDA/TZ6

GPIO33/SCLA/EPWMSYNCO/ADCSOCBO

GPIO14/TZ3/SCITXDB/SPICLKB

V

SS

V

DD

V

DD1A18

V

SS1AGND

V

SSA2

V

DDA2

GPIO15/TZ4

/SCIRXDB/SPISTEB

V

SSAIO

GPIO32/SDAA/EPWMSYNCI/ADCSOCAO

GPIO13/TZ2/CANRXB/SPISOMIB

V

DD3VFL

V

SS

V

DD

GPIO28/SCIRXDA/TZ5

V

SS

V

SS

V

DD

V

SS

V

DDIO

GPIO26/ECAP3/EQEP2I/SPICLKB

TEST2

TEST1

GPIO25/ECAP2/EQEP2B/SPISOMIB

XCLKIN

X1

X2

EMU1

EMU0

GPIO24/ECAP1/EQEP2A/SPISIMOB

GPIO27/ECAP4/EQEP2S/SPISTEB

TDO

GPIO30/CANRXA

GPIO31/CANTXA

ADCINA7

ADCINA6

ADCINA5

ADCINA4

ADCINA3

ADCINA2

ADCINA1

ADCINA0

ADCLO

ADCINB0

ADCINB1

ADCINB2

ADCINB3

ADCINB4

ADCINB5

ADCINB6

ADCINB7

ADCREFIN

ADCREFM

ADCREFP

ADCRESEXT

GPIO34

GPIO1/EPWM1B/SPISIMOD

GPIO2/EPWM2A

GPIO3/EPWM2B/SPISOMID

TMS320F2809, TMS320F2808, TMS320F2806

TMS320F2802, TMS320F2801, TMS320C2802

TMS320C2801, TMS320F28016, TMS320F28015

SPRS230L–OCTOBER 2003–REVISED DECEMBER 2009

www.ti.com

2.1 Pin Assignments

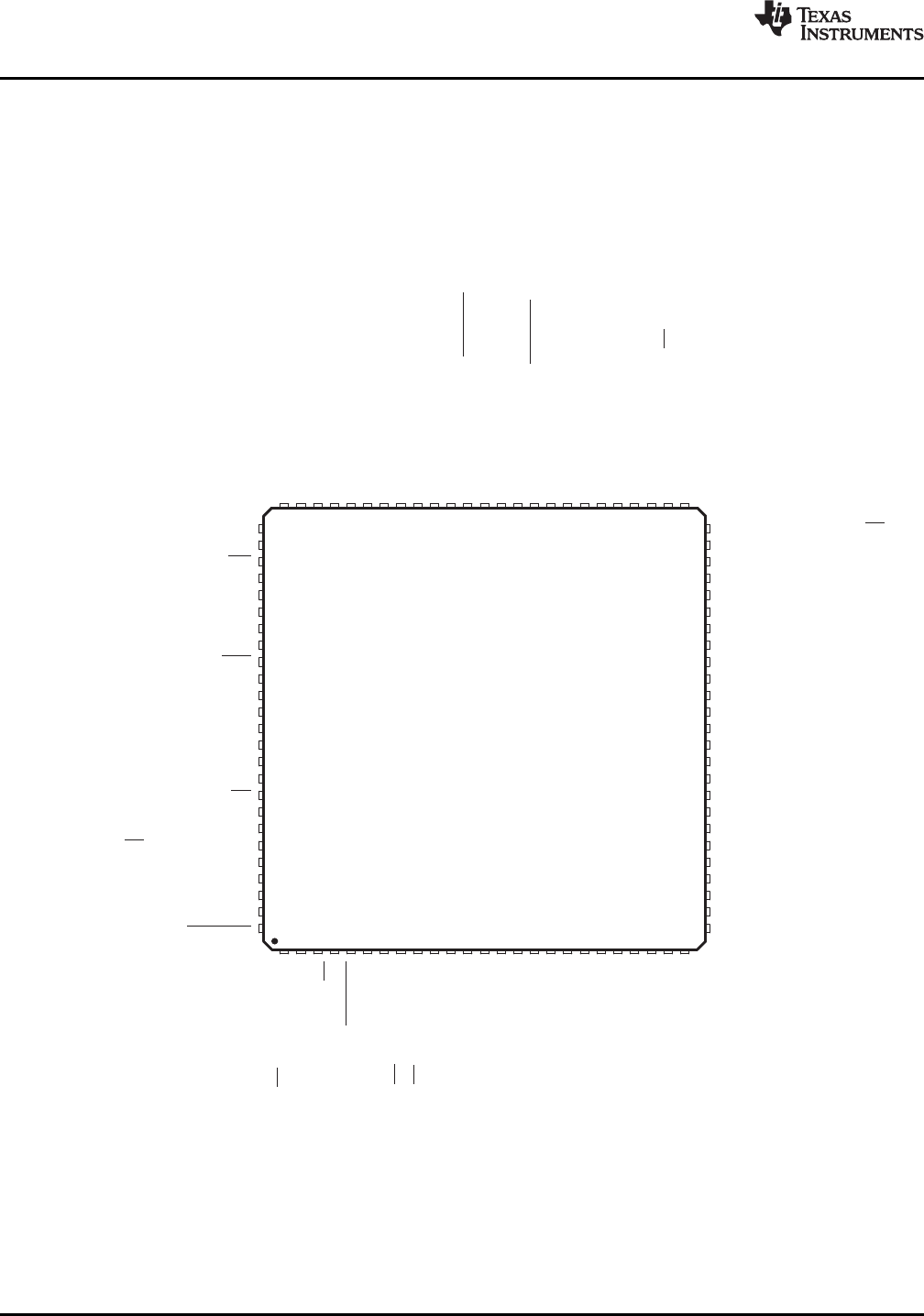

The TMS320F2809, TMS320F2808, TMS320F2806, TMS320F2802, TMS320F2801, TMS320C2802,

TMS320C2801, TMS320F28015, and TMS320F28016 100-pin PZ low-profile quad flatpack (LQFP) pin

assignments are shown in Figure 2-1, Figure 2-2, Figure 2-3, and Figure 2-4. The 100-ball GGM and ZGM

ball grid array (BGA) terminal assignments are shown in Figure 2-5. Table 2-3 describes the function(s) of

each pin.

Figure 2-1. TMS320F2809, TMS320F2808 100-Pin PZ LQFP (Top View)

14 Introduction Copyright © 2003–2009, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320F2809 TMS320F2808 TMS320F2806 TMS320F2802 TMS320F2801 TMS320C2802

TMS320C2801 TMS320F28016 TMS320F28015