TMS320F2809, TMS320F2808, TMS320F2806

TMS320F2802, TMS320F2801, TMS320C2802

TMS320C2801, TMS320F28016, TMS320F28015

www.ti.com

SPRS230L–OCTOBER 2003–REVISED DECEMBER 2009

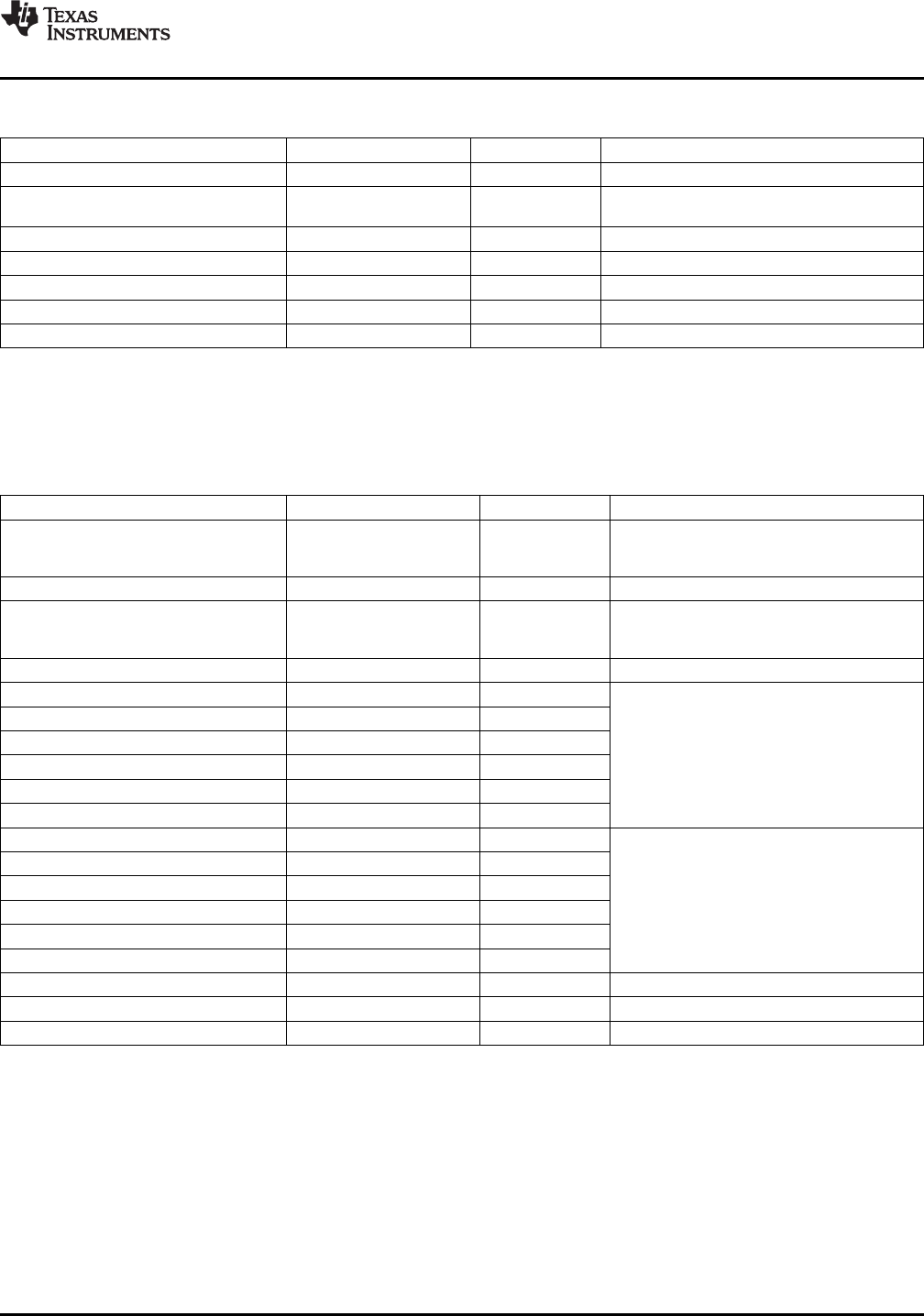

Table 3-8. Peripheral Frame 0 Registers

(1) (2)

NAME ADDRESS RANGE SIZE (x16) ACCESS TYPE

(3)

Device Emulation Registers 0x0880 – 0x09FF 384 EALLOW protected

EALLOW protected

FLASH Registers

(4)

0x0A80 – 0x0ADF 96

CSM Protected

Code Security Module Registers 0x0AE0 – 0x0AEF 16 EALLOW protected

ADC Result Registers (dual-mapped) 0x0B00 – 0x0B0F 16 Not EALLOW protected

CPU-TIMER0/1/2 Registers 0x0C00 – 0x0C3F 64 Not EALLOW protected

PIE Registers 0x0CE0 – 0x0CFF 32 Not EALLOW protected

PIE Vector Table 0x0D00 – 0x0DFF 256 EALLOW protected

(1) Registers in Frame 0 support 16-bit and 32-bit accesses.

(2) Missing segments of memory space are reserved and should not be used in applications.

(3) If registers are EALLOW protected, then writes cannot be performed until the EALLOW instruction is executed. The EDIS instruction

disables writes to prevent stray code or pointers from corrupting register contents.

(4) The Flash Registers are also protected by the Code Security Module (CSM).

Table 3-9. Peripheral Frame 1 Registers

(1) (2)

NAME ADDRESS RANGE SIZE (x16) ACCESS TYPE

Some eCAN control registers (and selected

eCANA Registers 0x6000 – 0x60FF 256 bits in other eCAN control registers) are

EALLOW-protected.

eCANA Mailbox RAM 0x6100 – 0x61FF 256 Not EALLOW-protected

Some eCAN control registers (and selected

eCANB Registers 0x6200 – 0x62FF 256 bits in other eCAN control registers) are

EALLOW-protected.

eCANB Mailbox RAM 0x6300 – 0x63FF 256 Not EALLOW-protected

ePWM1 Registers 0x6800 – 0x683F 64

ePWM2 Registers 0x6840 – 0x687F 64

ePWM3 Registers 0x6880 – 0x68BF 64

Some ePWM registers are EALLOW

protected. See Table 4-2.

ePWM4 Registers 0x68C0 – 0x68FF 64

ePWM5 Registers 0x6900 – 0x693F 64

ePWM6 Registers 0x6940 – 0x697F 64

eCAP1 Registers 0x6A00 – 0x6A1F 32

eCAP2 Registers 0x6A20 – 0x6A3F 32

eCAP3 Registers 0x6A40 – 0x6A5F 32

Not EALLOW protected

eCAP4 Registers 0x6A60 – 0x6A7F 32

eQEP1 Registers 0x6B00 – 0x6B3F 64

eQEP2 Registers 0x6B40 – 0x6B7F 64

GPIO Control Registers 0x6F80 – 0x6FBF 128 EALLOW protected

GPIO Data Registers 0x6FC0 – 0x6FDF 32 Not EALLOW protected

GPIO Interrupt and LPM Select Registers 0x6FE0 – 0x6FFF 32 EALLOW protected

(1) The eCAN control registers only support 32-bit read/write operations. All 32-bit accesses are aligned to even address boundaries.

(2) Missing segments of memory space are reserved and should not be used in applications.

Copyright © 2003–2009, Texas Instruments Incorporated Functional Overview 41

Submit Documentation Feedback

Product Folder Link(s): TMS320F2809 TMS320F2808 TMS320F2806 TMS320F2802 TMS320F2801 TMS320C2802

TMS320C2801 TMS320F28016 TMS320F28015