TMS320F2809, TMS320F2808, TMS320F2806

TMS320F2802, TMS320F2801, TMS320C2802

TMS320C2801, TMS320F28016, TMS320F28015

www.ti.com

SPRS230L–OCTOBER 2003–REVISED DECEMBER 2009

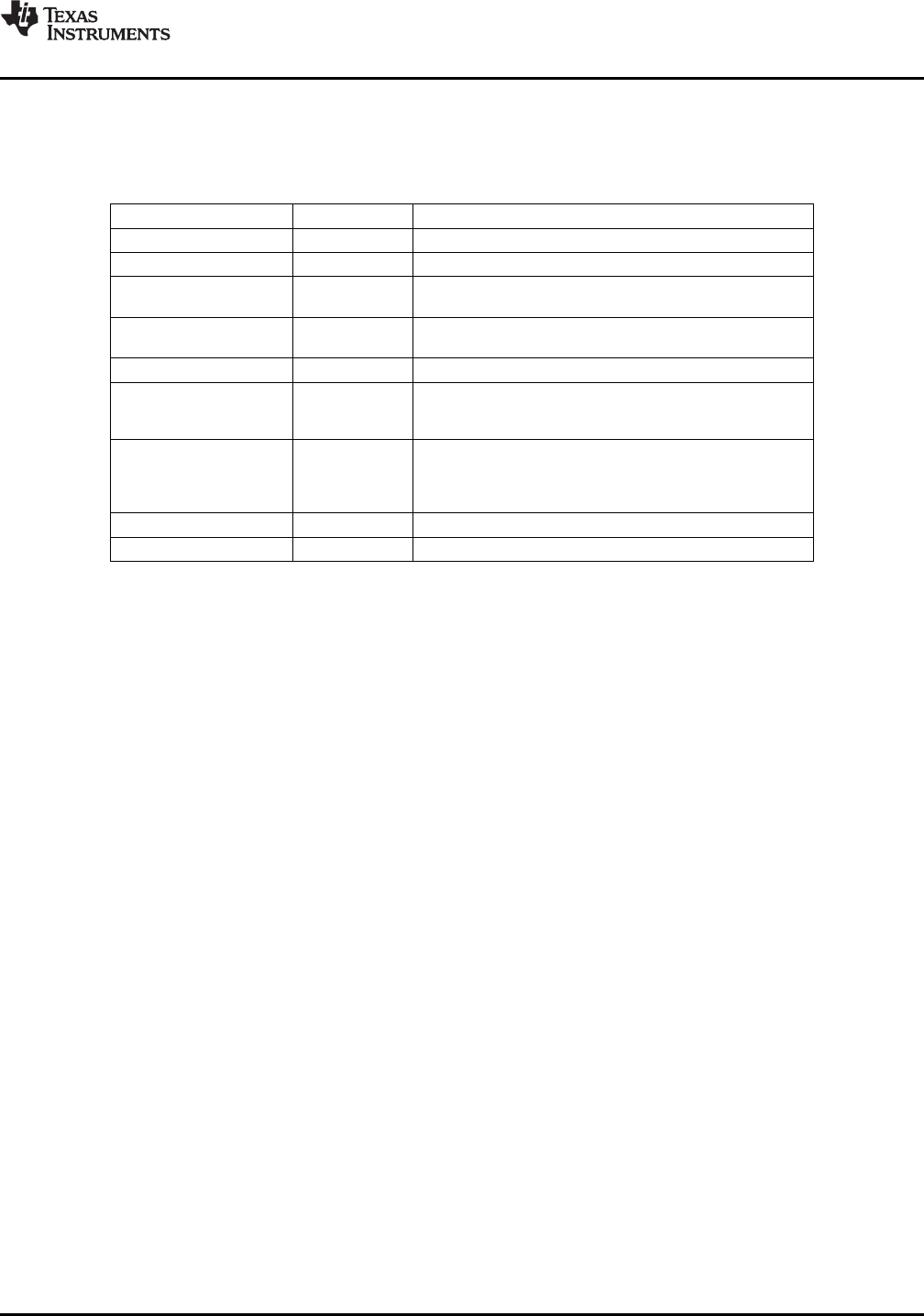

The wait-states for the various spaces in the memory map area are listed in Table 3-6.

Table 3-6. Wait-states

AREA WAIT-STATES COMMENTS

M0 and M1 SARAMs 0-wait Fixed

Peripheral Frame 0 0-wait Fixed

0-wait (writes) Fixed. The eCAN peripheral can extend a cycle as needed.

Peripheral Frame 1

2-wait (reads) Back-to-back writes will introduce a 1-cycle delay.

0-wait (writes)

Peripheral Frame 2 Fixed

2-wait (reads)

L0 & L1 SARAMs 0-wait

Programmed via the Flash registers. 1-wait-state operation

Programmable,

OTP is possible at a reduced CPU frequency. See Section 3.2.5

1-wait minimum

for more information.

Programmed via the Flash registers. 0-wait-state operation

Programmable, is possible at reduced CPU frequency. The CSM password

Flash

0-wait minimum locations are hardwired for 16 wait-states. See

Section 3.2.5 for more information.

H0 SARAM 0-wait Fixed

Boot-ROM 1-wait Fixed

Copyright © 2003–2009, Texas Instruments Incorporated Functional Overview 33

Submit Documentation Feedback

Product Folder Link(s): TMS320F2809 TMS320F2808 TMS320F2806 TMS320F2802 TMS320F2801 TMS320C2802

TMS320C2801 TMS320F28016 TMS320F28015