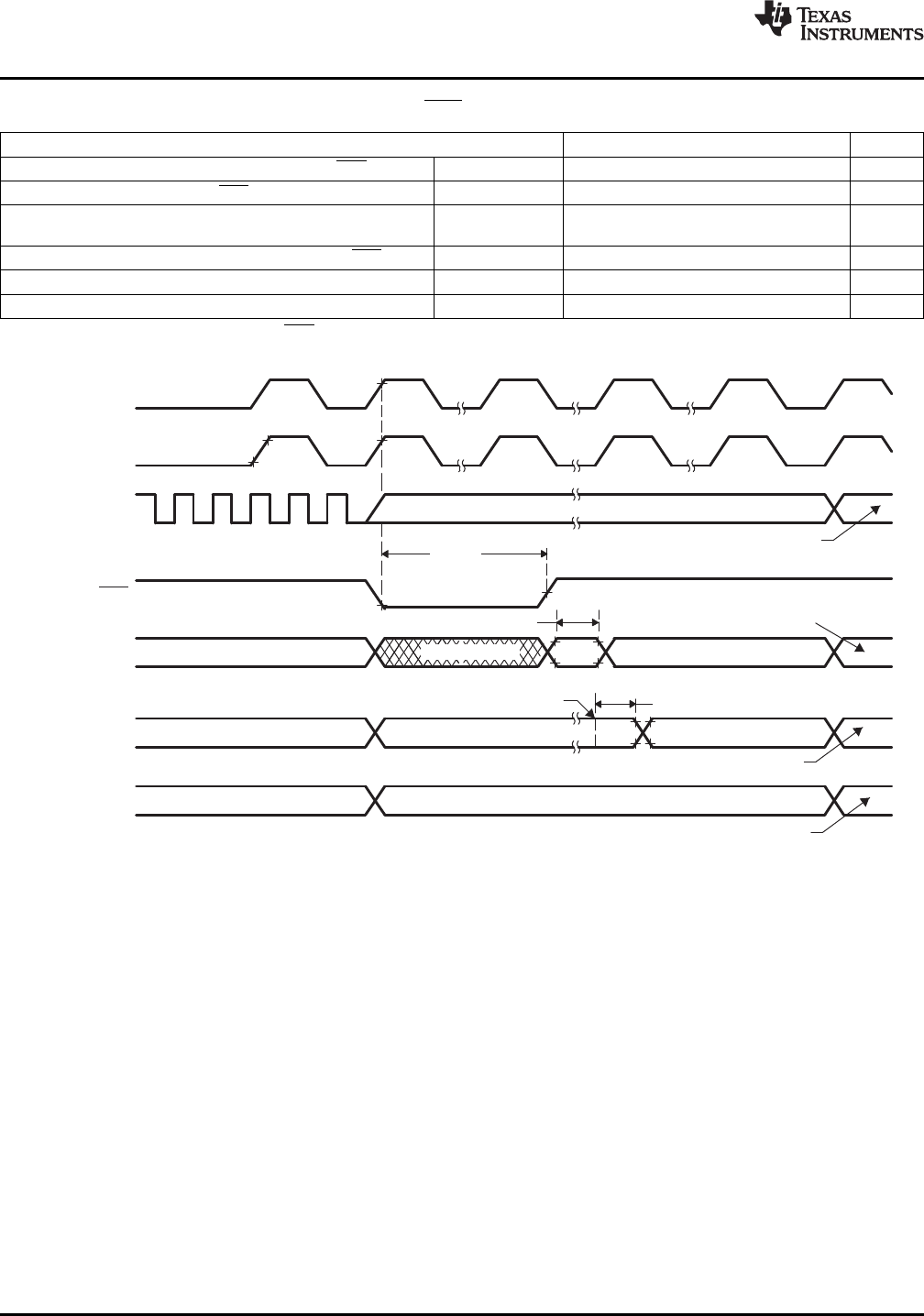

t

h(boot-mode)

(A)

t

w(RSL2)

XCLKIN

X1/X2

XRS

Boot-Mode

Pins

XCLKOUT

I/O Pins

Address/Data/

Control

(Internal)

Boot-ROM Execution Starts

User-Code Execution Starts

User-Code Dependent

User-Code Execution Phase

(Don’t Care)

User-Code Dependent

User-Code Execution

Peripheral/GPIO Function

User-Code Dependent

GPIO Pins as Input (State Depends on Internal PU/PD)

GPIO Pins as Input

Peripheral/GPIO Function

t

d(EX)

OSCCLK * 5

OSCCLK/8

TMS320F2809, TMS320F2808, TMS320F2806

TMS320F2802, TMS320F2801, TMS320C2802

TMS320C2801, TMS320F28016, TMS320F28015

SPRS230L–OCTOBER 2003–REVISED DECEMBER 2009

www.ti.com

Table 6-13. Reset (XRS) Timing Requirements

MIN NOM MAX UNIT

t

w(RSL1)

(1)

Pulse duration, stable XCLKIN to XRS high 8t

c(OSCCLK)

cycles

t

w(RSL2)

Pulse duration, XRS low Warm reset 8t

c(OSCCLK)

cycles

Pulse duration, reset pulse generated by

t

w(WDRS)

512t

c(OSCCLK)

cycles

watchdog

t

d(EX)

Delay time, address/data valid after XRS high 32t

c(OSCCLK)

cycles

t

OSCST

(2)

Oscillator start-up time 1 10 ms

t

h(boot-mode)

Hold time for boot-mode pins 200t

c(OSCCLK)

cycles

(1) In addition to the t

w(RSL1)

requirement, XRS has to be low at least for 1 ms after V

DD

reaches 1.5 V.

(2) Dependent on crystal/resonator and board design.

A. After reset, the Boot ROM code samples BOOT Mode pins. Based on the status of the Boot Mode pin, the boot code

branches to destination memory or boot code function. If Boot ROM code executes after power-on conditions (in

debugger environment), the Boot code execution time is based on the current SYSCLKOUT speed. The

SYSCLKOUT will be based on user environment and could be with or without PLL enabled.

Figure 6-9. Warm Reset

108 Electrical Specifications Copyright © 2003–2009, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320F2809 TMS320F2808 TMS320F2806 TMS320F2802 TMS320F2801 TMS320C2802

TMS320C2801 TMS320F28016 TMS320F28015