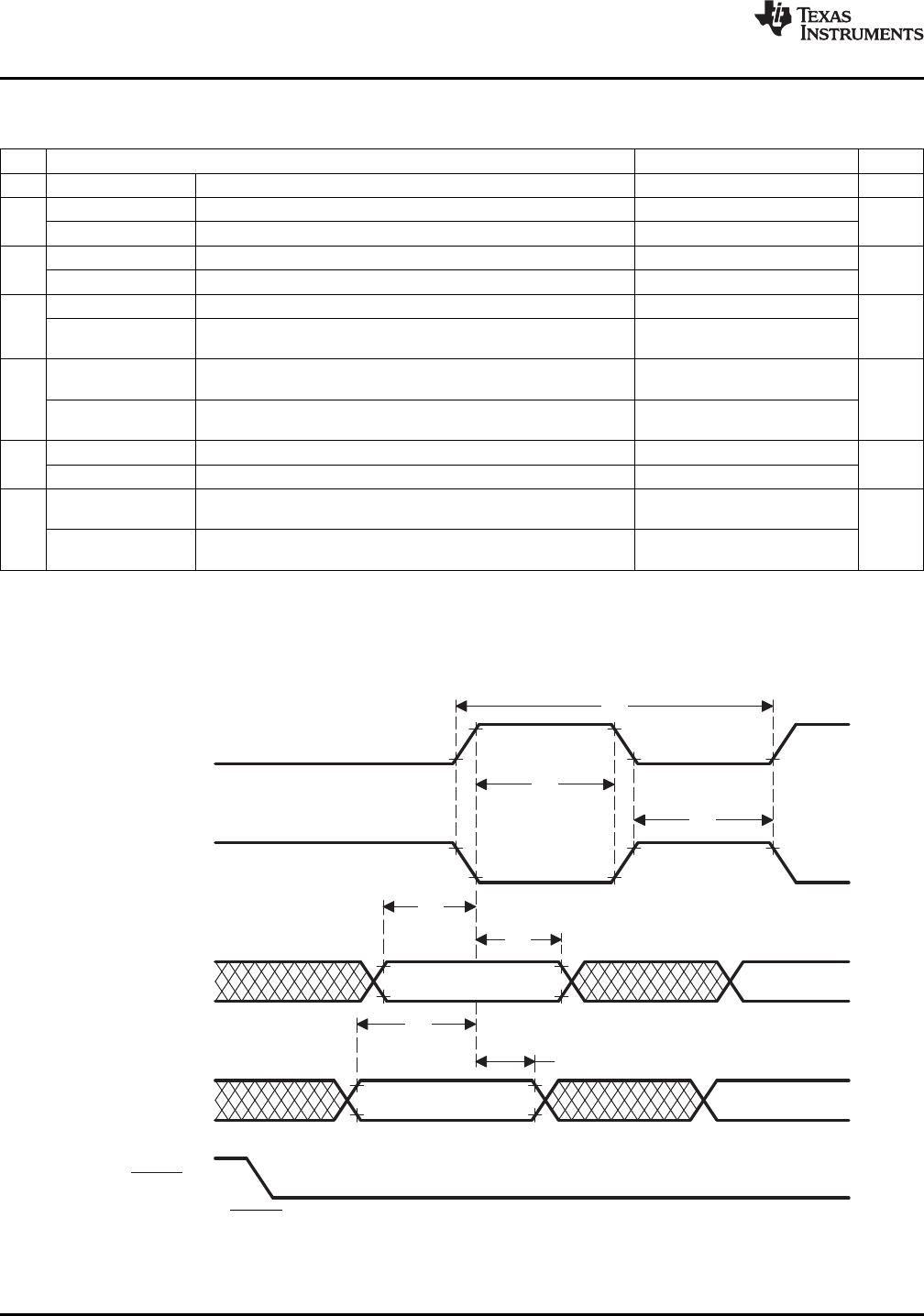

Data Valid

22

SPISIMO

SPISOMI

SPICLK

(clock polarity = 1)

SPICLK

(clock polarity = 0)

SPISIMO Data

Must Be Valid

SPISOMI Data Is Valid

21

12

18

17

14

13

SPISTE

(A)

TMS320F2809, TMS320F2808, TMS320F2806

TMS320F2802, TMS320F2801, TMS320C2802

TMS320C2801, TMS320F28016, TMS320F28015

SPRS230L–OCTOBER 2003–REVISED DECEMBER 2009

www.ti.com

Table 6-37. SPI Slave Mode External Timing (Clock Phase = 1)

(1) (2) (3) (4)

NO. MIN MAX UNIT

12 t

c(SPC)S

Cycle time, SPICLK 8t

c(LCO)

ns

t

w(SPCH)S

Pulse duration, SPICLK high (clock polarity = 0) 0.5t

c(SPC)S

– 10 0.5t

c(SPC)S

13 ns

t

w(SPCL)S

Pulse duration, SPICLK low (clock polarity = 1) 0.5t

c(SPC)S

– 10 0.5t

c(SPC) S

t

w(SPCL)S

Pulse duration, SPICLK low (clock polarity = 0) 0.5t

c(SPC)S

– 10 0.5t

c(SPC) S

14 ns

t

w(SPCH)S

Pulse duration, SPICLK high (clock polarity = 1) 0.5t

c(SPC)S

– 10 0.5t

c(SPC)S

t

su(SOMI-SPCH)S

Setup time, SPISOMI before SPICLK high (clock polarity = 0) 0.125t

c(SPC)S

17 ns

t

su(SOMI-SPCL)S

Setup time, SPISOMI before SPICLK low 0.125t

c(SPC)S

(clock polarity = 1)

t

v(SPCL-SOMI)S

Valid time, SPISOMI data valid after SPICLK low 0.75t

c(SPC)S

(clock polarity = 1)

18 ns

t

v(SPCH-SOMI)S

Valid time, SPISOMI data valid after SPICLK high 0.75t

c(SPC) S

(clock polarity = 0)

t

su(SIMO-SPCH)S

Setup time, SPISIMO before SPICLK high (clock polarity = 0) 35

21 ns

t

su(SIMO-SPCL)S

Setup time, SPISIMO before SPICLK low (clock polarity = 1) 35

t

v(SPCH-SIMO)S

Valid time, SPISIMO data valid after SPICLK high 0.5t

c(SPC)S

– 10

(clock polarity = 0)

22 ns

t

v(SPCL-SIMO)S

Valid time, SPISIMO data valid after SPICLK low 0.5t

c(SPC)S

– 10

(clock polarity = 1)

(1) The MASTER / SLAVE bit (SPICTL.2) is cleared and the CLOCK PHASE bit (SPICTL.3) is cleared.

(2) t

c(SPC)

= SPI clock cycle time = LSPCLK/4 or LSPCLK/(SPIBRR + 1)

(3) Internal clock prescalers must be adjusted such that the SPI clock speed is limited to the following SPI clock rate:

Master mode transmit 25-MHz MAX, master mode receive 12.5-MHz MAX

Slave mode transmit 12.5-MHz MAX, slave mode receive 12.5-MHz MAX.

(4) The active edge of the SPICLK signal referenced is controlled by the CLOCK POLARITY bit (SPICCR.6).

A. In the slave mode, the SPISTE signal should be asserted low at least 0.5t

c(SPC)

before the valid SPI clock edge and

remain low for at least 0.5t

c(SPC)

after the receiving edge (SPICLK) of the last data bit.

Figure 6-23. SPI Slave Mode External Timing (Clock Phase = 1)

124 Electrical Specifications Copyright © 2003–2009, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320F2809 TMS320F2808 TMS320F2806 TMS320F2802 TMS320F2801 TMS320C2802

TMS320C2801 TMS320F28016 TMS320F28015