Philips Semiconductors Product data sheet

SC28L91

3.3 V or 5.0 V Universal Asynchronous

Receiver/Transmitter (UART)

2004 Oct 21

35

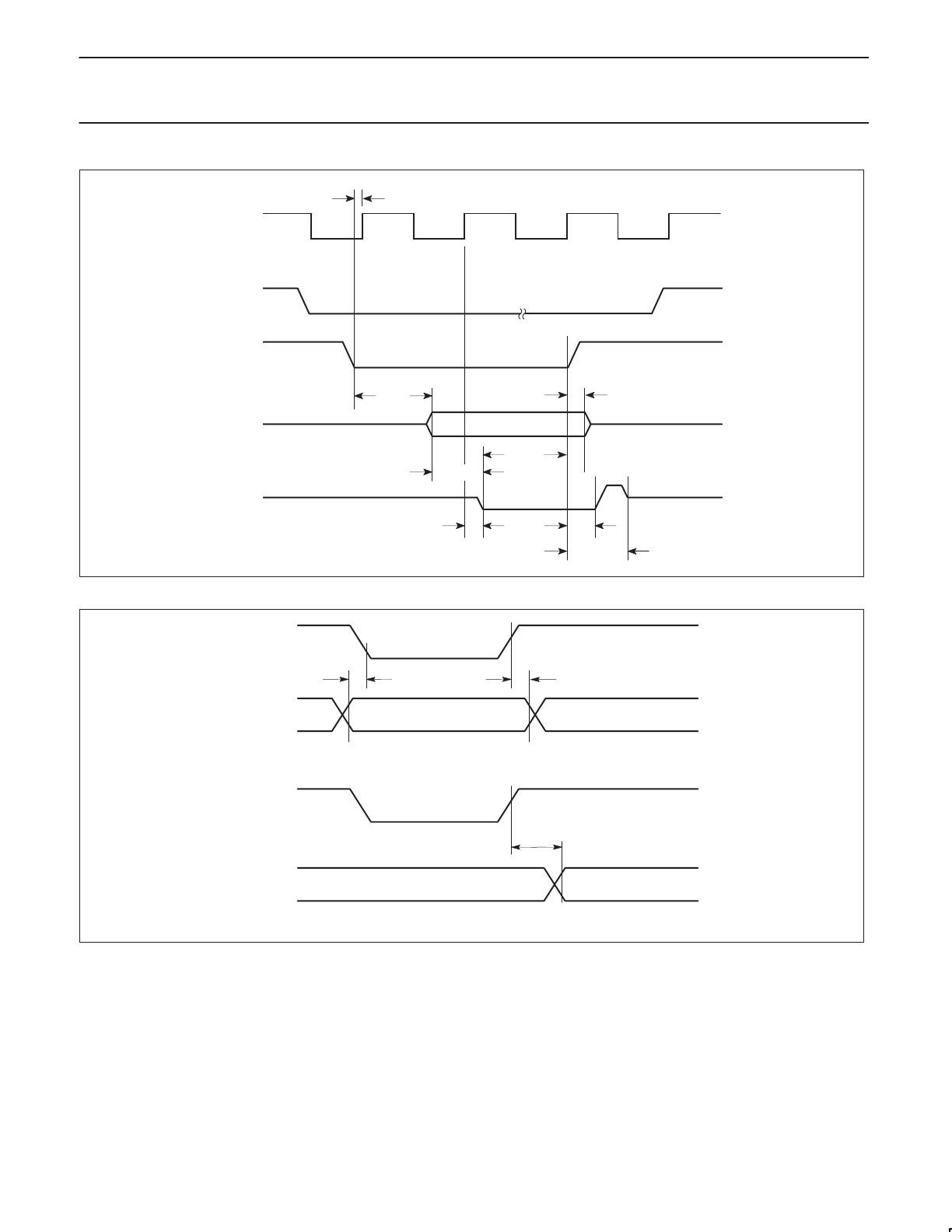

X1/CLK

INTRN

IACKN

D0–D7

DTACKN

t

CSC

t

DD

t

DF

t

CSD

t

DAL

t

DCR

t

DAH

t

DAT

NOTE: DACKN low requires two rising edges of X1 clock after CSN is low.

SD00149

Figure 8. Interrupt Cycle Timing (68XXX mode)

(b) OUTPUT PINS

RDN

IP0–IP6

WRN

OP0–OP7

t

PS

t

PH

t

PD

OLD DATA NEW DATA

(a) INPUT PINS

SD00135

Figure 9. Port Timing