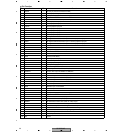

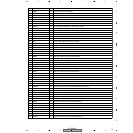

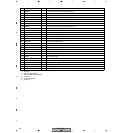

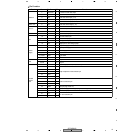

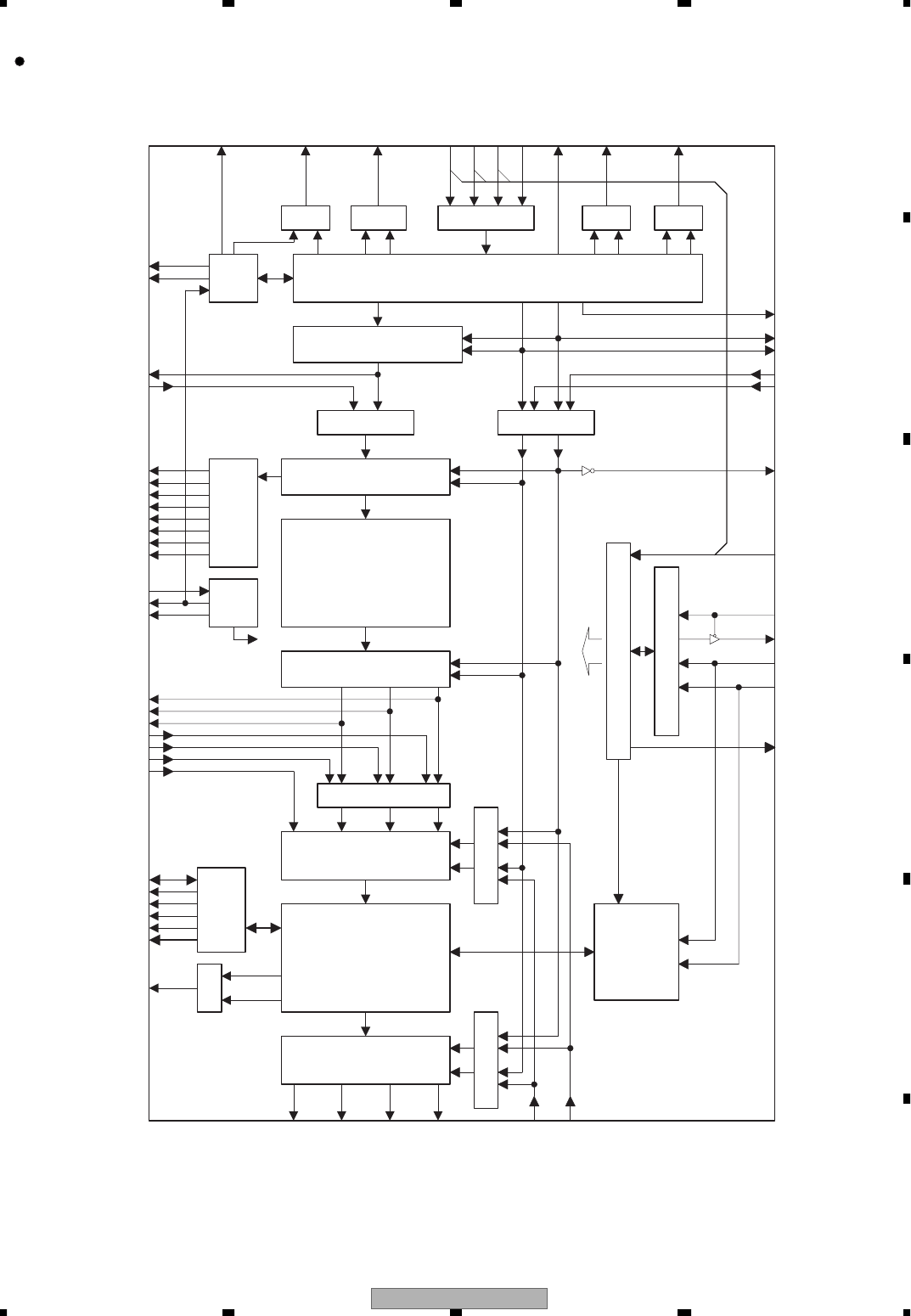

SE-DIR800C

35

5678

56

7

8

C

D

F

A

B

E

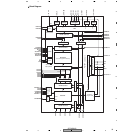

Block Diagram

DIRMCK

DDIN0

DDIN1

DDIN2

DDIN3

DDINSEL

V

ERR/BS

DBL/V

DIRINT

PLL DIR

DIRO Interface

DIRBCK

DIRWCK

SDIASEL

SDIA Interface

SDIACKSEL

SDWCKI0

SDBCKI0

/SDBCKO

CRC

DIRPCO

DIRSDO

SDIA

SURENC

KARAOKE

MUTE

CRC

AC3DATA

DTSDATA

NONPCM

ZEROFLG

XI

XO

CPO

PLL

Clock for DIR

Block (25MHz)

Clock for DSP

Block (30MHz)

SDOA Interface

MainDSP

(AC-3/ProLogicII/DTS decoder)

SDIB Interface

SDOA0

SDOA1

SDOA2

L,R

LS,RS

C,LFE

SDIB0

SDIB1

SDIB2

SDIB3

SDIBSEL

SDIBCKSEL

External Memory

Interface

SubDSP

RAMD0-15

CASN

RASN

RAMWEN

RAMOEN

RAMA0-17

OVFB/END

SDOB Interface

SDOBCKSEL

SDOB3

SDOB2

SDOB1

SDOB0

SDWCKI1

SDBCKI1

OPORT0-7

Coefficient /

Program RAM

MPLOAD

/CS

SO

SI

SCK

IPORT0-4

Control Signal

DBL

Control Register

Microprocessor I/F

VMOD BSMOD

ERR

BS

SYNC

U

FS128

C

SYNC/U

FS128/C

UMOD CMOD

OVFSEL

OVFB

END

7 6 5 IPORT5-7

DIRPRO

/LOCK