Appendix B Timing Signal Information

NI PXI-4224 User Manual B-8 ni.com

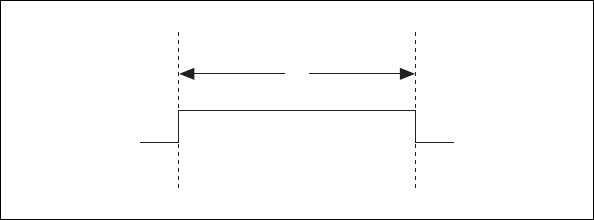

Figure B-10. AI CONV CLK Output Signal Timing

The ADC switches to hold mode within 60 ns of the selected edge. This

hold-mode delay time is a function of temperature and does not vary from

one conversion to the next. Separate the AI CONV CLK pulses by at least

one conversion period.

The NI PXI-4224 sample interval counter generates AI CONV CLK

unless you select an external source. The AI SAMP CLK signal starts the

counter, which counts down and reloads itself until the scan finishes. The

counter then reloads itself in preparation for the next AI SAMP CLK pulse.

A/D conversions generated by an internal or external AI CONV CLK

signal are inhibited unless they occur within a sequence. Scans occurring

within a sequence can be gated by either the hardware AI PAUSE TRIG

signal or the software command register gate.

AI PAUSE TRIG Signal

PFI 0, PXI_Trig<0..5>, or PXI_Star can externally input the

AI PAUSE TRIG signal, which is not available as an output on the

I/O connector. AI PAUSE TRIG can mask off scans in a sequence.

You can configure the pin you select as the source for AI PAUSE TRIG in

level-detection mode. You can configure the polarity selection for the pin

as either active high or active low.

In level-detection mode, the AI SAMP CLK signal is masked off and no

scans can occur.

AI PAUSE TRIG can neither stop a scan in progress nor continue a

previously gated-off scan. In other words, once a scan has started,

AI PAUSE TRIG does not gate off conversions until the beginning of the

next scan. Conversely, if conversions are gated off, AI PAUSE TRIG does

not gate them back on until the beginning of the next scan.

t

w

= 50 to 100 ns

t

w