Appendix B Timing Signal Information

NI PXI-4224 User Manual B-6 ni.com

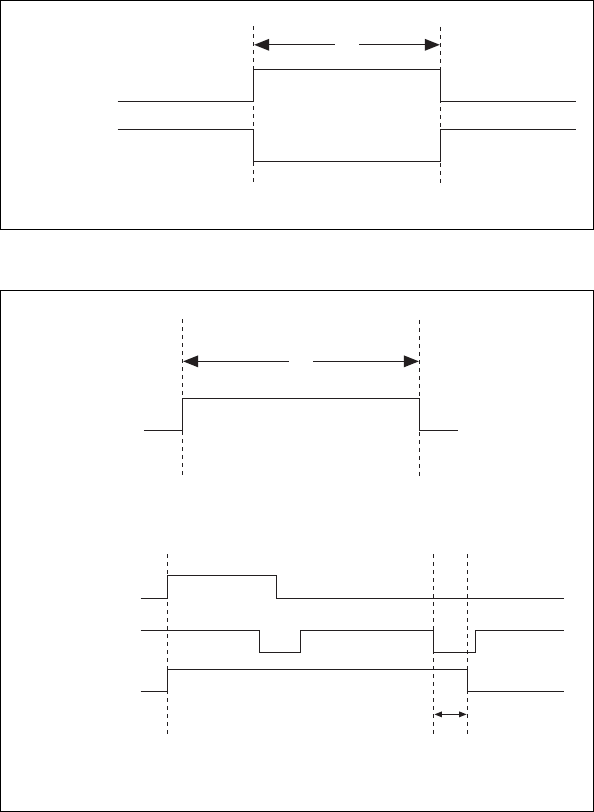

Figures B-7 and B-8 show the input and output timing requirements

forAISAMPCLK.

Figure B-7. AI SAMP CLK Input Signal Timing

Figure B-8. AI SAMP CLK Output Signal Timing

The AI CONV CLK pulses are masked off until the device generates

AI SAMP CLK. If you use internally generated conversions, the first

AI CONV CLK appears when the onboard SI2 counter reaches zero.

If you select an external AI CONV CLK, the first external pulse after

Rising-Edge

Polarity

Falling-Edge

Polarity

t

w

= 10 ns minimum

t

w

b. Scan in Progress, Two Conversions per Scan

Start Pulse

AI CONV REF

AI SAMP CLK

t

off

= 10 ns minimum t

off

t

w

= 50 to 100 ns

t

w

a. Start of Scan

AI SAMP CLK