Appendix B Timing Signal Information

© National Instruments Corporation B-5 NI PXI-4224 User Manual

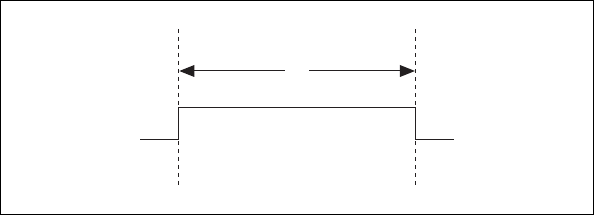

Figure B-6. AI REFTRIG Output Signal Timing

AI SAMP CLK Signal

The AI SAMP CLK signal can be externally input from PFI 0,

PXI_Trig<0..5>, or PXI_Star. It can be output on any PXI trigger bus line.

Refer to Figures B-1 and B-2 for the relationship of AI SAMP CLK to the

sequence.

As an input, AI SAMP CLK is configured in edge-detection mode. You can

configure the polarity selection for either rising or falling edge. The

selected edge of AI SAMP CLK initiates a scan. The SI2 counter starts if

you select an internally triggered AI CONV CLK.

As an output, AI SAMP CLK reflects the actual start pulse that initiates

a scan, even if the starts are externally triggered by another PFI or

PXI_Trig<0..5>. Two output options are available. The first option is an

active high pulse with a pulse width of 50 to 100 ns, which indicates the

start of the scan. The second option is an active high pulse that terminates

at the start of the last conversion in the scan, which indicates a scan in

progress. AI SAMP CLK is deasserted, t

off

, after the last conversion in the

scan is initiated. This output is set to high-impedance at startup.

t

w

= 50 to 100 ns

t

w