ESMT M12L64164A

Elite Semiconductor Memory Technology Inc. Publication Date: Mar. 2003

Revision: 1.7 1/44

SDRAM

1M x 16 Bit x 4 Banks

Synchronous DRAM

FEATURES

JEDEC standard 3.3V power supply

LVTTL compatible with multiplexed address

Four banks operation

MRS cycle with address key programs

- CAS Latency (2 & 3)

- Burst Length (1, 2, 4, 8 & full page)

- Burst Type (Sequential & Interleave)

All inputs are sampled at the positive going edge of the

system clock

DQM for masking

Auto & self refresh

64ms refresh period (4K cycle)

ORDERING INFORMATION

54 Pin TSOP (Type II)

(400mil x 875mil )

PRODUCT NO. MAX FREQ. PACKAGE

M12L64164A-6T 166MHz

M12L64164A-7T 143MHz

TSOP II

GENERAL DESCRIPTION

The M12L64164A is 67,108,864 bits synchronous high data rate Dynamic RAM organized as 4 x 1,048,576 words by

16 bits. Synchronous design allows precise cycle controls with the use of system clock I/O transactions are possible on

every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same

device to be useful for a variety of high bandwidth, high performance memory system applications.

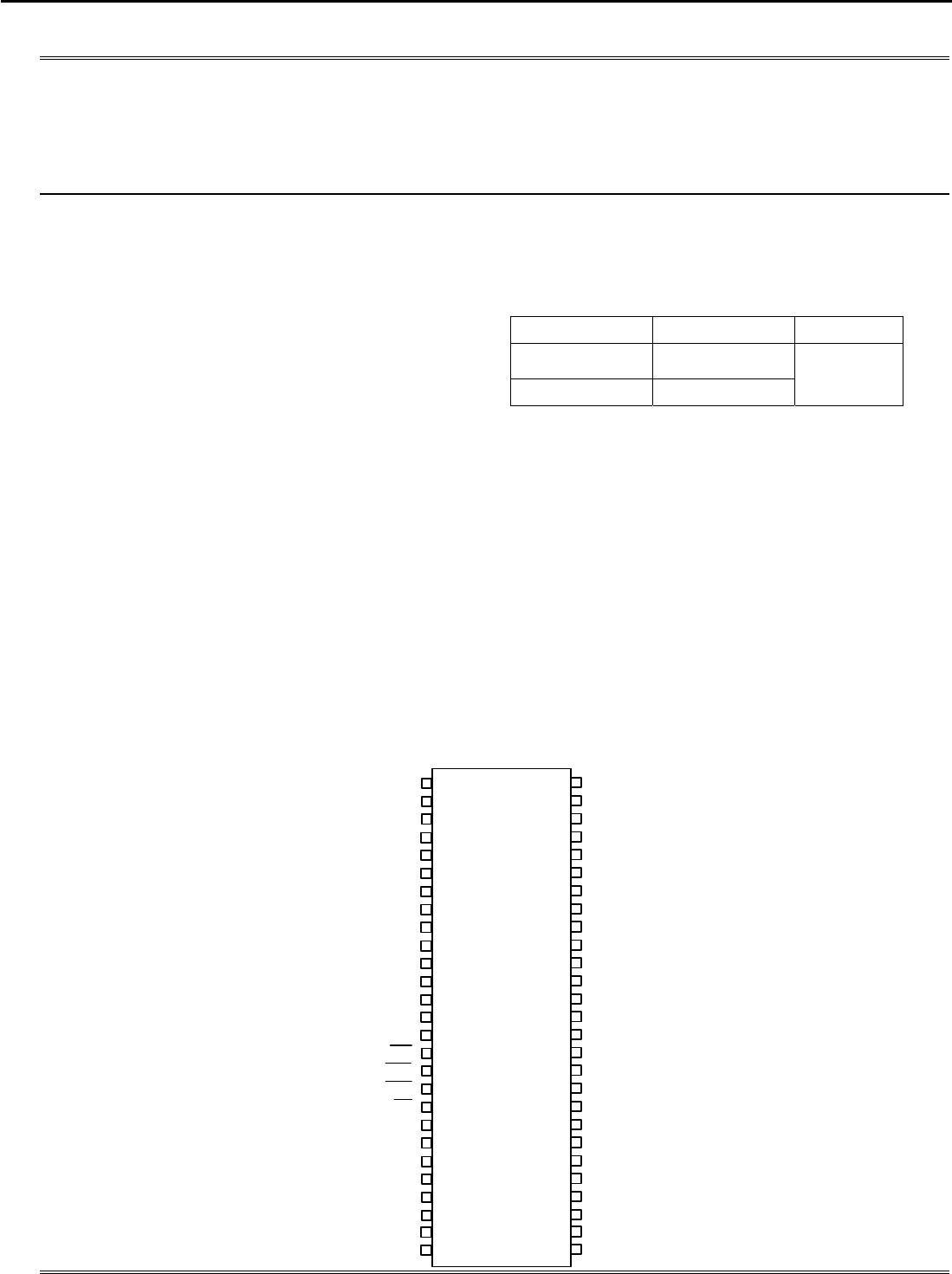

PIN ASSIGNMENT

Top View

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

V

DD

DQ0

V

DDQ

DQ1

DQ2

V

SSQ

DQ3

DQ4

V

DDQ

DQ5

DQ6

V

SSQ

DQ7

V

DD

LDQM

WE

CAS

RAS

CS

A

13

A12

A10/AP

A

0

A1

A2

A3

VDD

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

V

SS

DQ15

V

SSQ

DQ14

DQ13

V

DDQ

DQ12

DQ11

V

SSQ

DQ10

DQ9

V

DDQ

DQ8

V

SS

NC

UDQM

CLK

CKE

NC

A

11

A9

A8

A7

A6

A5

A4

VSS

DVD47 harman/kardon

46