HCD-MD373

41 41

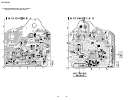

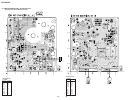

6-2. BLOCK DIAGRAMS

– BD (CD) SECTION –

E

F

A

B

C

D

A

C

RF

FF

TE

D

B

E

F

LD

PD

VCC

VC

RF

SUMMING

AMP

FOCUS

ERROR

AMP

TRACKING

ERROR

AMP

LD

DRIVE

Q101

VC

BUFFER

INTEG-

RATOR

RF EQ

AMP

INTEG-

RATOR

DIGITAL

PLL

IC101

DIGITAL SERVO

DIGITAL SIGNAL PROCESSOR

SUBCODE

PROCESSOR

SERIAL IN

INTERFACE

SERVO

AUTO

SEQUENCER

SERVO

INTERFACE

OVER SAMPLING

DIGITAL FILTER

D/A

INTERFACE

DIGITAL

OUT

TIMING

LOGIC

ERROR

CORRECTOR

EFM

DEMODULATION

APCLD/PD

AMP

5

7

8

6

16

14 49

51

13

LDON

VC

22

1521

12

11

10

3

IC103

RF AMP

VC

4

VREF

HOLD SW

REF

IC102

FOCUS/TRACKING COIL DRIVE

SPINDLE/SLED MOTOR DRIVE

11

12

T+

T–

14

13

F+

F–

TRACKING

COIL

FOCUS

COIL

CH2OUTR

CH2OUTF

5

CH2FIN

6

CH2RIN

2

CH1FIN

3

CH1RIN

23

CH3RIN

24

CH3FIN

25

CH4SIN

27

CH4BIN

20

MUTE

CH1OUTF

CH1OUTR

17

18

SD+

SD–

CH3OUTF

CH3OUTR

M

15

16

SP+

SP–

CH4OUTF

CH4OUTR

M

M102

SLED

MOTOR

M101

SPINDLE

MOTOR

TFDR

TRDR

FFDR

FRDR

SRDR

SFDR

VC

FD

PD

LASER

DIODE

A

C

D

B

E

F

DETECTOR

OPTICAL PICK-UP BLOCK

(KSS-213BA/NP)

LD

POWER

RF AC

ASY1

48

38

42

43

39

41

40

28

26

29

ASY0

ASYMMETRY

CORRECTION

SFDR

MDP

SRDR

33

32

FRDR

FFDR

31

30

42

TRDR

TFDR

SE

CE

TE

FE

RFDC

CE

VC

SLED

PWM

GENERATOR

FOCUS

PWM

GENERATOR

TRACKING

PWM

GENERATOR

PWM

GENERATOR

SLED

SERVO

FOCUS

SERVO

TRACKING

SERVO

SERVO DSP

DIGITAL

CLV

OPERATIONAL

AMPLIFIER

ANALOG

SWITCH

A/D

CONVERTER

16K

RAM

DATA BUS

3rd ORDER

NOISE SHAPER

PWM PWM

CPU

INTERFACE

2

1

3

SQSO

60

D OUT

67

STAO

66

XTA1

8

SENS

20

SCOR

14

XLON

XRST

SQCK

5

DATA

6

XLAT

7

CLOK

32

56

19

59

81

58

82

9

SCLK 33

27

SSTP

79

RMUT

80

LMUT

70

LMUT

71

AIN1

72

LOUT1

77

LOUT2

76

AIN2

75

LOUT2

CD-L

(L-OUT)

R OUT

HOLD

+5V

SQCK

SCOR

CLOK

XLT

DATA

SENS

SQSO

XRST

DOUT

X101

16.9344MHz

MAIN

SECTION

09

S101

LIMIT SW

• SIGNAL PATH

: CD

: CD (Digital out)

57

C

(Page 44)