22

ONYX 800R

ONYX 800R

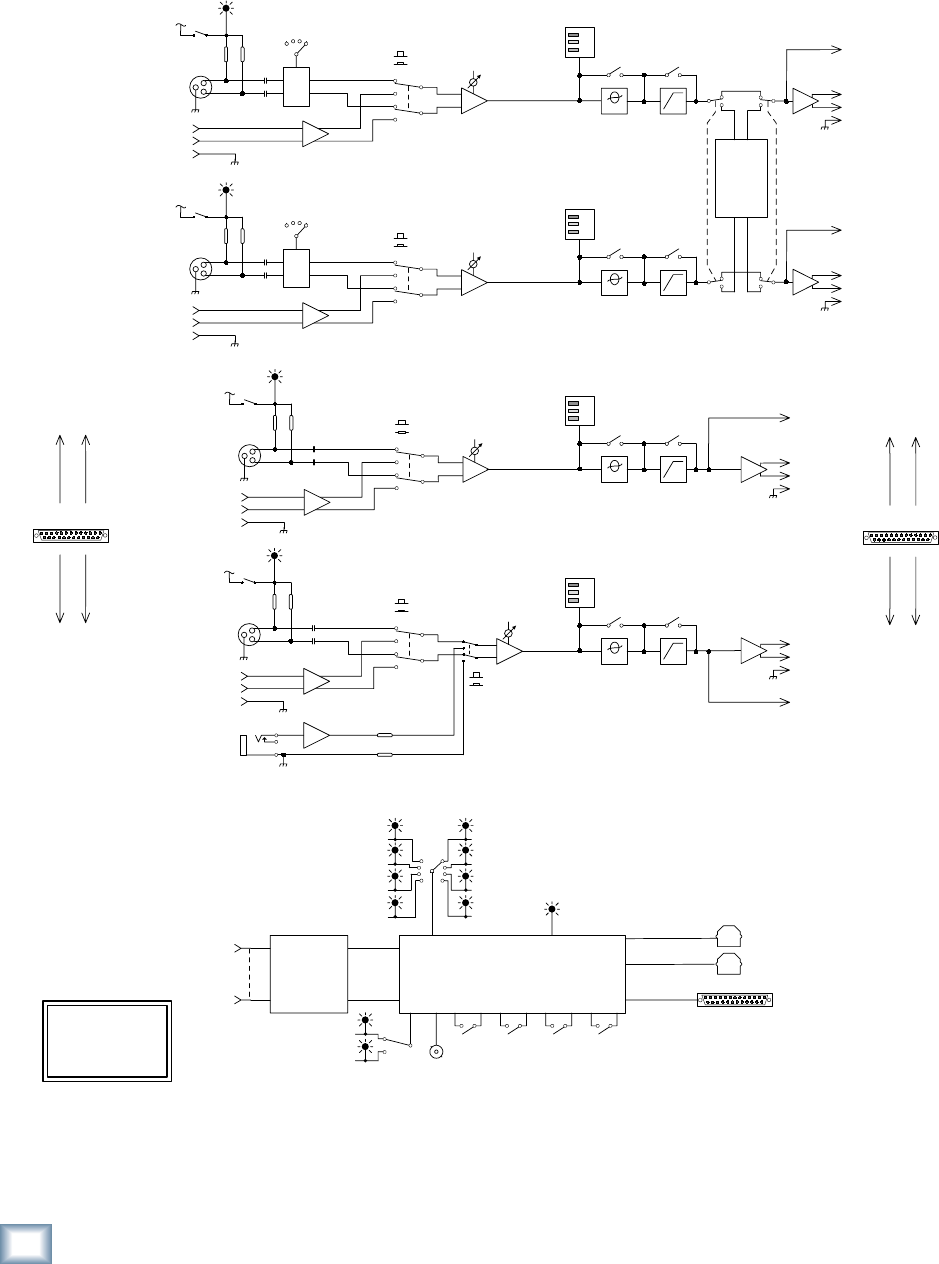

Onyx 800R Block Diagram

Line Inputs

to A/D

+

–

Line Out

to A/D

+

–

Line Out

Low Cut

Phase

to A/D

+

–

Line Out

to A/D

+

–

Line Out

Line Outputs

M/S

Matrix

Ch 1/Left

Ch 2/Right

Word Clock

Input

ADAT

Optical

Out

2

1

S/PDIF

AES/EBU

Out

FPGA

Sample Rate

24-bit

Lock

Impedance

75Ω/110Ω

75Hz

88.2 kHz

48 kHz

44.1 kHz

32 kHz

96 kHz

176.4 kHz

192 kHz

External

Dithered 16-bit

Ch 1

Ch 8

A/D

Conversion

Pro/

Consumer

Single/

Dual

Wire

ADAT

ADAT

48V

Channel 1

Mic

Line

Gain

Mic: 0 to +60 dB

Line: –20 to +40 dB

Hi-Z

Mic/Line

Hi-Z

+

-

2

3

1

3

0

0

5

0

0

1

3

0

0

2

4

0

0

Mic

Impedance

Line

Mic

+

-

+

-

48V

Channel 2

Mic

Line

Gain

Mic: 0 to +60 dB

Line: –20 to +40 dB

2

3

1

3

0

0

5

0

0

1

3

0

0

2

4

0

0

Mic

Impedance

Line

Mic

+

-

+

-

48V

Channels 3-6

Mic

Line

Gain

Mic: 0 to +60 dB

Line: –20 to +40 dB

Hi-Z: –20 to +40 dB

2

3

1

Line

Mic

+

-

48V

Channels 7-8

Mic

Line

2

3

1

Line

Mic

+

-

+

-

OL

0

-20

Low Cut

Phase

75Hz

OL

0

-20

Low Cut

Phase

75Hz

OL

0

-20

Low Cut

Phase

75Hz

OL

0

-20

Word Clock

Termination

Off/75Ω

MACKIE

ONYX 800R

BLOCK DIAGRAM

(#04/21/04_DF)