MZ-NH700/NHF800

3232

MZ-NH700/NHF800

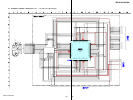

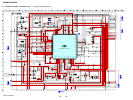

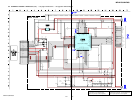

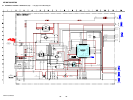

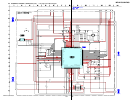

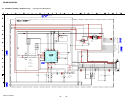

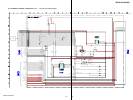

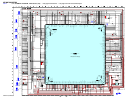

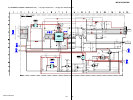

6-11. SCHEMATIC DIAGRAM – MAIN Section (8/9) –

• See page 40 for IC Pin Function Description.

• See page 24 for Waveforms.

R825

C803

R857

C810

C817

C814

C812

C832

C833

R840

C857

R820

C809

R817

R812

C804

C805

R821

R818R819

C

82

8

R869

IC804

R845

Q802

C822 C823C853

C818

C820

C819

FB801

X801

R802

C811

C839

C835

FB807

R809

R863

R864

FB802

FB809

FB810

R855

R856

R860

R843

C847

R842

R876

R832

R822

R862

C856

R867

C821

R823

SL802

R

8

0

6

R

8

0

1

C843

R839

R804

R805

C

8

0

1

C

8

0

2

R868

C859

R841

R808

X802

R

8

0

7

Q803

R866

C808

R815

R811

Q801

C850

L803 L804

C816

C846

C845

L801

R824

L805

D801

R833

R858

C827

S

L

8

0

1

D803

R829

C861

R837

IC801

R879R878

R880

R813

R

8

2

6

C

8

3

6

C

83

8

C864

R861

R

8

2

7

F

B

80

3

VDR801

C830

R865

L802

R830

R810

CL8001

CL8027

CL8055

0

0.01

470k

0.1

0.1

0.1

1

1

1

0

22p

220

0.1

1k

100k

0.01

0.47

2.2M

2.2k 1k

10

0

0p

0

XC61CC2502NR

0

XP152A12C0MR

0.1 0.10.1

10

6.3V

0.1

47

6.3V

0

48MHz

0

0.1

0.1

0.1

0

0

0

220

0

0

0

0

10

2.2k

0.1

47k

0

10k

1M

1M

0.1

1M

0.1

10k

4

.7

k

4

.7

k

0.1

0

22

22

7

p

7

p

0

0.1

10

4.7k

22.5792MHz

2

.2

k

2SC4738F-Y/GR

(TPL3)

0

1

220k

10k

2SK1830-TE85L

0.1

10 10

47

6.3V

0.1

47

6.3V

0

0

MA2Z748001S0

0

47k

0.1

MA2SD32008S0

0

0.1

2.2k

CXD2681-223GG

4747

47

220

0

1

0

6

.3

V

1

0

6

.3

V

0.1

22

1

0

0

1000p

470k

0

0

K1

K2

K3

K4

K5

K6

AOUTL

AOUTR

XHP_STBY

MUTE

BEEP

VBUS_VB_CTL

UDP

UDM

XCS_REC_DRV

VBUS_DET

EFM_CLK

EFM

RECP

SUSPEND

USB_HOLD

GND_SW

VBUS_MON

LC_DRV1

LC_DRV2

PLSE_XDC

XLDON

PEAK

BOTM

OFTRK

TE

FE

ABCD

VREF

XRST_RF

SSB_DATA

SSB_CLK

ADIP

S_MON

APCREF_DA

VC

RFI

MDVCC_CTL

VIN

XRST_MTR_DRV

SLD_MON_W

SLD_MON_V

SLD_MON_U

SLD_PWM

SLD_CON_U

SLD_CON_V

SLD_CON_W

CLV_MON_W

CLV_MON_V

CLV_MON_U

CLV_PWM

CLV_CON_U

CLV_CON_V

CLV_CON_W

TF1

TR1

ZI2

ZI1

FR1

FF1

MINUS_MON

A_FS256

REGO3

CHG_MON

CHG_I_CTL2

CHG_I_CTL3

CHG_PWM

HIDC_MON

CHG_TYPE2

SDO0

SCK0

XCS_ADC

XBCK

LRCK

FS256

ADDT

XOPT_CTL

DIN1

XJACK_DET

OPT_DET

XPD_ADC

GND

S0

S1

V

B

F

C

R

A

M

V

D

D

R

E

G

5

_

R

E

G

FCRAMVDD

XMIC_DET

BEEP

MUTE

XHP_STBY

AOUTR

AOUTL

VBUS_MON

V

B

U

S

_

V

B

_

C

T

L

GND_SW

AOUTR

AOUTL

VIN

APCREF_DA

E

F

M

_

C

L

K

FF1

TF1

TR1

FR1

4FS

SLD_PWM

CLV_CON_U

ADIP

XRST

HALF_LOCK

REC_KEY

RST_CONT

RMC_KEY

WK_DET

REG5_VSTB

SET_KEY_1

SET_KEY_2

VREF

REG5_VSTB

TE

S_MON

VC

FE

ABCD

BOTM

PEAK

RFI

XCS_REG_DRV

VBUS_DET

SSB_DATA

SSB_CLK

PLSE_XDC

X

C

S

_

N

V

X

C

S

_

L

C

D

X

C

S

_

P

W

R

_

IC

C

L

V

_

C

O

N

_

U

X

R

S

T

2

X

H

O

L

D

_

S

W

V

R

E

C

_

S

E

L

X

R

S

T

_

R

F

S

L

E

E

P

S

L

D

_

C

O

N

_

U

S

D

I1

M

U

T

E

X

H

P

_

S

T

B

Y

M

D

V

C

C

_

C

T

L

B

E

E

P

S

C

K

0

S

D

O

0

S

D

I0

R

E

G

5

_

R

E

G

WK_DET

L

C

D

_

R

S

T

POEN_CLOSE_SW

P

R

O

T

E

C

T

P

A

U

S

E

E

F

M

O

F

T

R

K

S

L

D

_

C

O

N

_

U

S

L

D

_

C

O

N

_

W

S

L

D

_

C

O

N

_

V

S

L

D

_

M

O

N

_

V

S

L

D

_

M

O

N

_

W

C

L

V

_

M

O

N

_

W

C

L

V

_

M

O

N

_

V

C

L

V

_

M

O

N

_

U

C

L

V

_

C

O

N

_

W

C

L

V

_

C

O

N

_

V

C

L

V

_

P

W

M

S

L

D

_

M

O

N

_

U

MINUS_MON

A

_

F

S

2

5

6

LC_DRV1

LC_DRV2

EFM_CLK

EFM

RECP

SUSPEND

USB_HOLD

VBUS_DET

XCS_REC_DRV

XRST_MTR_DRV

SLD_CON_W

SLD_CON_V

SLD_CON_U

SLD_PWM

SLD_MON_U

SLD_MON_V

SLD_MON_W

TF1

TR1

ZI2

ZI1

FR1

FF1

CLV_CON_W

CLV_CON_V

CLV_CON_U

CLV_PWM

CLV_MON_U

CLV_MON_V

CLV_MON_W

USB_HOLD

SUSPEND

XLDON

PLSE_XDC

LC_DRV1

LC_DRV2

PEAK

BOTM

OFTRK

TE

FE

ABCD

VREF

XRST_RF

SSB_DATA

SSB_CLK

ADIP

S_MON

APCREF_DA

VC

RFI

MDVCC_CTL

A_FS256

VIN

R

E

G

4

_

D

V

D

D

3.3V

REG_F

REG5_VSTB

REG5_OSC

REG5_REG

REG5_REG

JOG_A

JOG_B

HIMD_PROTECT

ZI2

ZI1

REG_DACVREFM

XLDON

VBUS_VB_CTL

GND_SW

VBUS_MON

MINUS_MON

X

R

S

T

_

M

T

R

_

D

R

V

R

E

C

P

S

C

K

1

S

D

O

1

CHG_MON

CHG_MON

C

H

G

_

I_

C

T

L

2

C

H

G

_

I_

C

T

L

3

CHG_I_CTL2

CHG_I_CTL3

C

H

G

_

P

W

M

CHG_PWM

HIDC_MON

HIDC_MON

CHG_TYPE2

CHG_TYPE2

SCK0

SDO0

XBCK

LRCK

FS256

XCS_ADC

ADDT

DIN1

XJACK_DET

OPT_DET

R

M

C

_

D

T

C

K

XOPT_CTL

X

O

P

T

_

C

T

L

XPD_ADC

X

P

D

_

A

D

C

X

C

S

_

A

D

C

X

J

A

C

K

_

D

E

T

O

P

T

_

D

E

T

D

IN

1

S0

S1

FS256

ADDT

LRCK

XBCK

S

1

S

0

RADIO_ON

DRAM_HOLD_DET

DRAM_VDD_CLR

D

R

A

M

_

A

L

O

N

E

F

F

C

L

R

X

M

IC

_

D

E

T

XMIC_DET

VOUT

VIN

VSS

NC

D

V

D

D

1

_

0

D

V

S

S

1

_

0

D

V

D

D

1

_

1

D

V

S

S

1

_

1

D

V

D

D

1

_

2

D

V

S

S

1

_

2

D

V

D

D

1

_

3

D

V

S

S

1

_

3

D

V

D

D

1

_

4

D

V

S

S

1

_

4

D

V

D

D

1

_

5

D

V

S

S

1

_

5

D

V

D

D

1

_

6

D

V

S

S

1

_

6

D

V

D

D

1

_

7

D

V

S

S

1

_

7

D

V

D

D

1

_

8

D

V

S

S

1

_

8

D

V

D

D

1

_

9

D

V

S

S

1

_

9

D

V

D

D

1

_

1

0

D

V

S

S

1

_

1

0

D

V

D

D

1

_

1

1

D

V

S

S

1

_

1

1

D

V

D

D

3

V

S

S

_

3

A

V

D

D

1

A

A

V

S

S

1

A

A

V

D

D

1

B

A

V

S

S

1

B

A

V

D

D

1

C

A

V

D

D

2

D

V

D

D

2

5

S

V

A

D

A

V

S

S

2

A

V

D

D

3

A

V

S

S

3

A

V

D

D

4

A

A

V

S

S

4

A

A

V

D

D

4

B

A

V

S

S

4

B

A

V

D

D

4

C

A

V

S

S

4

C

A

V

D

D

5

A

V

S

S

5

A

V

D

D

6

A

V

S

S

6

D

A

V

D

D

D

V

D

D

2

5

L

P

F

D

A

V

S

S

O

S

C

V

D

D

U

S

B

O

S

C

V

D

D

T

S

M

V

D

D

M

A

IF

V

D

D

M

S

JT

A

G

V

D

D

U

S

B

IF

V

D

D

V

S

S

_

0

V

S

S

_

1

V

S

S

_

2

IF

V

D

D

_1

IF

V

D

D

_

2

IF

V

D

D

_

3

IFV

D

D

_

4

IF

V

S

S

_

1

IF

V

S

S

_2

D

R

A

M

V

D

D

0

D

R

A

M

V

S

S

0

D

R

A

M

V

D

D

1

D

R

A

M

V

D

D

2

D

R

A

M

VD

D

3

D

R

A

M

V

D

D

4

D

R

A

M

V

S

S

1

D

R

A

M

V

S

S

2

FC

R

A

M

V

D

D

0

F

C

R

A

M

V

S

S

0

FC

R

A

M

V

D

D

1

F

C

R

A

M

V

S

S

1

F

V

D

D

0

F

V

S

S

0

S

R

A

M

V

D

D

0

S

R

A

M

V

S

S

0

UPUEN

UOSCI

UOSCO

SRAMVDD1

SRAMVSS1

EBIFVDD0

EBIFVSS0

EBIFVDD1

EBIFVSS1

EBIFVDD2

EBIFVSS2

EBIFVDD3

EBIFVSS3

EBIFVDD4

EBIFVSS4

EBIFVDD5

EBIFVSS5

EBIFVDD6

EBIFVSS6

EBIFVDD7

EBIFVSS7

ASYO

ASYI

RFI

PCO

FILI

FILO

CLTV

PEAK

BOTM

ABCD

FE

VC

ADIO

ADRB

SE

TE

AUX1

ADRT

DCHG

APC

ADC1EXTC

D_VREGO

VB_MON

CHG_MON

VREF_MON

SET_KEY_1

SET_KEY_2

DCIN_DET

HIDC_MON

WK_DET

VBUS_MON

RMC_KEY

RST_CONT

RADIO_ON

XRST

PLL2EXTCI

PLL2EXTCO

PLL3EXTCI

PLL3EXTCO

DACVREFH

APCREF_DA

ADC3VREFH

AD3EXTC

VIN

VREFL

AOUTL

AOUTR

VREFR

DCLSOUTR

DCLSOUTL

RTCK

ADFG

TFDR

FFDR

FRDR

FS4

SFDR

SPRD

S

P

FD

S

P

D

V

S

P

D

W

S

P

C

U

S

P

C

V

SP

C

W

S

L

C

U

S

L

C

V

D

IN

FS

2

5

6

_O

U

T

C

H

O

P

P

ER

C

L

K

M

N

T

0

M

N

T

1

M

N

T

2

M

N

T

3

O

F

T

R

K

R

E

C

P

S

L

C

W

S

R

D

R

S

L

DW

S

L

D

V

E

F

M

O

P

A

U

S

E

_

K

E

Y

P

R

O

T

E

C

T

O

P

T_

D

E

T

X

JA

C

K

_

D

E

T

X

M

IC

_

D

E

T

O

P

E

N

_

C

L

O

S

E

_

S

W

X

C

S

_

A

D

C

X

P

D

_

A

D

C

N

C

X

R

S

T

_

L

C

D

U

S

B

_

W

A

K

E

A

7

C

A

L

_

S

W

S

I0

S

O

0

S

C

K

0

X

G

U

M

_

O

N

B

E

E

P

X

O

P

T

_

C

T

L

L

A

M

_

R

E

Q

C

H

K

L

A

M

_

S

P

R

E

Q

M

D

V

C

C

_

C

T

L

V

B

U

S

_

V

B

_

C

T

L

L

A

M

_

N

A

M

E

P

F

0

S

I1

S

O

1

S

C

K

1

S

L

D

_

M

O

N

A

O

U

T

_

S

E

L

Y

U

Z

U

_

S

L

E

E

P

F

F

C

L

R

C

H

G

I_

C

T

L

1

C

H

G

I_

C

T

L

2

C

H

G

I_

C

T

L

3

S

L

B

U

S

Y

X

T

E

S

T

X

R

F

_

R

S

T

V

R

E

C

_

S

E

L

X

H

O

L

D

_

S

W

T

_

M

A

R

K

_

S

W

X

R

S

T

2

_

D

E

T

C

H

G

I_

S

E

L

R

E

C

P

_

M

O

N

S

P

D

L

_

M

O

N

X

C

S

_

P

W

R

_

IC

R

X

D

T

X

D

X

C

S

_

L

C

D

X

R

S

T

_

M

T

R

_

D

R

V

X

C

S

_

N

V

C

H

G

_

P

W

M

IAMP_CAL

NC

D_VCONT_PWM

CHG_OPR_LED

XCS_REC_DRV

GND_SW

CS_RTC

JOG_A

JOG_B

VBUS_DET

SSB_DATA

SSB_CLK

HIMD_PROTECT

LDPEN

CHG_TYPE2

AD2ENDF

TEST

SRAM_MODE

HSALF

TIGER_MON0

TIGER_MON1

TIGER_MON2

TIGER_MON3

TIGER_MON4

TIGER_MON5

TIGER_MON6

TIGER_MON7

TIGER_MON8

TIGER_MON9

XLSRCK

TAT

TAN

NAR

IDO

SAK

LRCKI

XBCKI

DATAI

SI3

SO3

SCK3

SI4

SO4

SCK4

SCS3

SCS4

HI_Z_SLD

HI_Z_SPDL

SET_CODE0

SET_CODE1

SET_CODE2

SET_CODE3

D_EN1

D_EN2

D_ENVG

DADT

PWM_L1

PWM_L2

JTAG0

JTAG1

CLKIN2

FS256

ADDT

LRCK

XBCK

OSCI

OSCO

FS512

DTCK

UDP

UDM

USBHOLD

SUSPEND

I2C_1

I2C_2

S

S

*

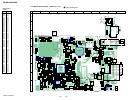

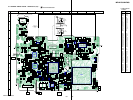

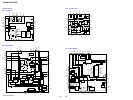

CSP(Chip Size Package)

SYSTEM CONTROLLER,DIGITAL SIGNAL PROCESSOR

SWITCH

WAKE UP

HALF_LOCK_SW/OPEN_SW

REC_KEY/DOWNLOAD

BATT_MINUS_MON

TRDR

R

E

C

_

L

E

D

/A

C

C

E

S

S

_

L

E

D

P

F

1

/S

0

D

O

P

F

2

/S

1

D

O

P

F

3

/R

T

G

3

X

M

U

T

E

/M

U

T

E

C

C

_

C

T

L

/V

I_

C

T

L

DRAM_HOLD_DET

DRAM_VDD_CLR

B+ SWITCH

Q801,802

+2.5V REGULATOR

(8/9)

(NHF800)

D

R

A

M

_

A

L

O

N

E

22µH

10µH

(Page 31)

(Page 33)

(Page 26)

(Page 28)

(Page 25)

(Page 27)

(Page 28)

(Page 30)

(Page 33)

(Page 33)

Ver 1.1