RS-A9/EW

116

1234

1234

C

D

F

A

B

E

208

207

206

205

204

203

202

201

200

199

198

197

196

195

194

193

192

191

189

188

187

186

185

184

183

182

181

180

190

179

178

177

175

174

173

172

171

170

176

169

168

167

165

164

163

162

161

160

159

158

157

166

71

72

73

74

75

76

77

78

79

80

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

81

82

83

84

86

87

88

89

90

85

91

92

93

94

96

97

98

99

95

100

101

102

103

104

5

4

3

2

7

6

9

8

1

14

13

12

11

16

15

17

10

19

18

23

22

21

20

25

24

27

26

29

28

32

31

30

34

33

36

35

40

39

38

37

41

43

42

45

44

50

49

48

47

46

52

51

152

153

154

155

150

151

156

148

149

143

144

145

146

141

142

140

147

138

139

134

135

136

137

132

133

130

131

128

129

125

126

127

123

124

121

122

120

117

118

119

116

114

115

112

113

107

108

109

110

111

105

106

BMSTR

1

IDENTIFIER

VDD

CS

SBTS

GND

WR

RD

GND

VDD

GND

REDY

SW

CPA

VDD

VDD

GND

ACK

MS0

MS1

GND

GND

MS2

MS3

FLAG11

VDD

FLAG10

FLAG9

FLAG8

GND

DATA0

DATA1

DATA2

VDD

DATA3

DATA4

DATA5

GND

DATA6

DATA7

DATA8

VDD

GND

VDD

DATA9

DATA10

DATA11

GND

DATA12

DATA13

NC

NC

DATA14

NC

IRQ2

IRQ1

IRQ0

GND

NC

NC

FLAG3

VDDVDD

RSF0

GND

RCLK0

DR0A

DR0B

TFS0

TCLK0

VDD

GND

DT0A

DT0B

RFS1

GND

RCLK1

DR1A

DR1B

TFS1

TCLK1

VDD

VDD

DT1A

DT1B

PWM

EVENT1

GND

PWM

EVENT0

BR1

BR2

VDD

CLKIN

XTAL

VDD

GND

SDCLK1

GND

VDD

SDCLK0

DMAR1

DMAR2

HBR

GND

RAS

SDWE

VDD

DQM

SDCKE

SDA10

GND

DMAG1

DMAG2

HBG

GND

GND

BMS

BSEL

TCK

GND

TMS

TDI

TRST

TDO

EMU

ID0

ID1

NC

VDD

VDD

GND

GND

VDD

VDD

GND

GND

VDD

VDD

GND

GND

VDD

DATA15

GND

VDD

VDD

FLAG2

FLAG1

FLAG0

GND

ADDR0

ADDR1

ADDR2

VDD

VDD

ADDR3

ADDR4

ADDR5

GND

GND

ADDR6

ADDR7

ADDR8

VDD

GND

ADDR9

ADDR10

ADDR11

GND

VDD

ADDR12

ADDR13

ADDR14

VDD

ADDR15

ADDR16

ADDR17

GND

GND

ADDR18

ADDR19

ADDR20

VDD

ADDR21

ADDR22

ADDR23

GND

VDD

RESET

CAS

DATA16

DATA17

DATA18

DATA19

DATA20

DATA22

DATA21

NC

DATA23

DATA24

DATA25

DATA26

DATA27

DATA28

DATA29

DATA30

DATA31

FLAG7

FLAG6

FLAG5

FLAG4

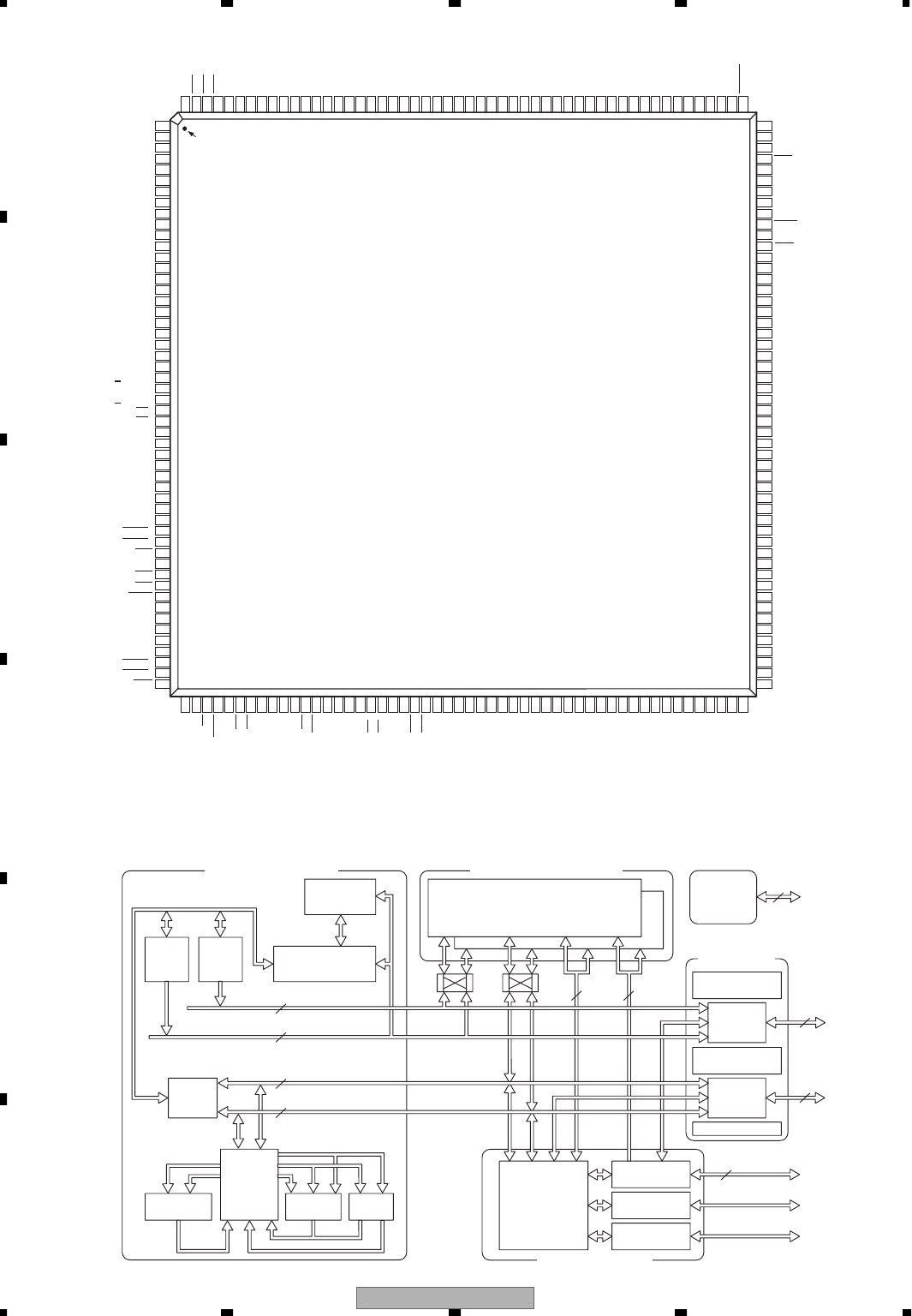

*ADSP-21065LCS-240

CORE PROCESSOR

DAG1

8x4x32

16x40 bit

Bus connect

(PX)

Multiplier

Parallel

shift

ALU

DAG2

8x4x24

Command cash

32x48 bit

Dual port block

Test and

emulation

PM address bus

DM address bus

PM data bus

DM data bus

24

7

24

32

4

(2 Rx,2Tx)

2

(I S)

2

(I S)

(2 Rx,2Tx)

32

48

40

Program •

sequence

IOP

Resistor

(memmory map)

Control,

Status,

Timmer and

Data buffer

Data •

Resistor •

File

SDRAM

Interface

Address Bus

MUX

Data bus

MUX

Host port

Multi proccesor

inter face

DMA

controller

SPORT0

SPORT1

Processor port

ADDR data

ADDR data ADDR

10A

17

10D

48

data

I/O port

Block 0

Block 1

data ADDR

DUAL PORT SRAM

JTAG

EXTERNAL

PORT

I/O PROCESSOR

- Block diagram