YMF744B

February 3, 1999

-54-

4-3. PCI Interface (Fig.3, 4)

Item Symbol Condition Min. Typ. Max. Unit

PCICLK Cycle Time t

PCYC

30 - - ns

PCICLK High Time t

PHIGH

11 - - ns

PCICLK Low Time t

PLOW

11 - - ns

PCICLK Slew Rate - 1 - 4 V/ns

t

PVAL

(Bused signal) 2 - 11 ns

PCICLK to Signal Valid Delay

t

PVAL

(

PTP

)

(Point to Point) 2 - 12 ns

Float to Active Delay t

PON

2--ns

Active to Float Delay t

POFF

--28ns

t

PSU

(Bused signal) 7 - - ns

*11 (Point to Point) 10 - - nsInput Setup Time to PCICLK

t

PSU

(

PTP

)

*12 (Point to Point) 12 - - ns

Input Hold Time for PCICLK t

PH

0--ns

Note : Top = 0-70°C, PVDD=3.3

±

0.3 V, VDD=3.3

±

0.3 V, CVDD=3.3

±

0.3 V, LVDD=3.3

±

0.3 V, C

L

=10 pF

*11: This characteristic is applicable to REQ# and PCREQ# signal.

*12: This characteristic is applicable to GNT# and PCGNT# signal.

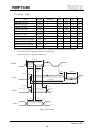

t

PCICLK

PCYC

t

PHIGH

0.3 VDD3

0.4 VDD3

0.5 VDD3

t

PLOW

Fig.3: PCI Clock timing

PCICLK

OUTPUT

INPUT

Tri-State

OUTPUT

1.5 V

1.5 V

1.5 V

t

PVAL

t

PON

t

POFF

t

PSU

t

PH

Fig.4: PCI Bus Signals timing