Digital Audio Interface (J51)

2-7

System Interfaces

2.5 Digital Audio Interface (J51)

The digital audio interface contains digital audio signal data (I2S), clocks etc.

Please see the TAS5066 data manual for signal timing and details not ex-

plained in this document.

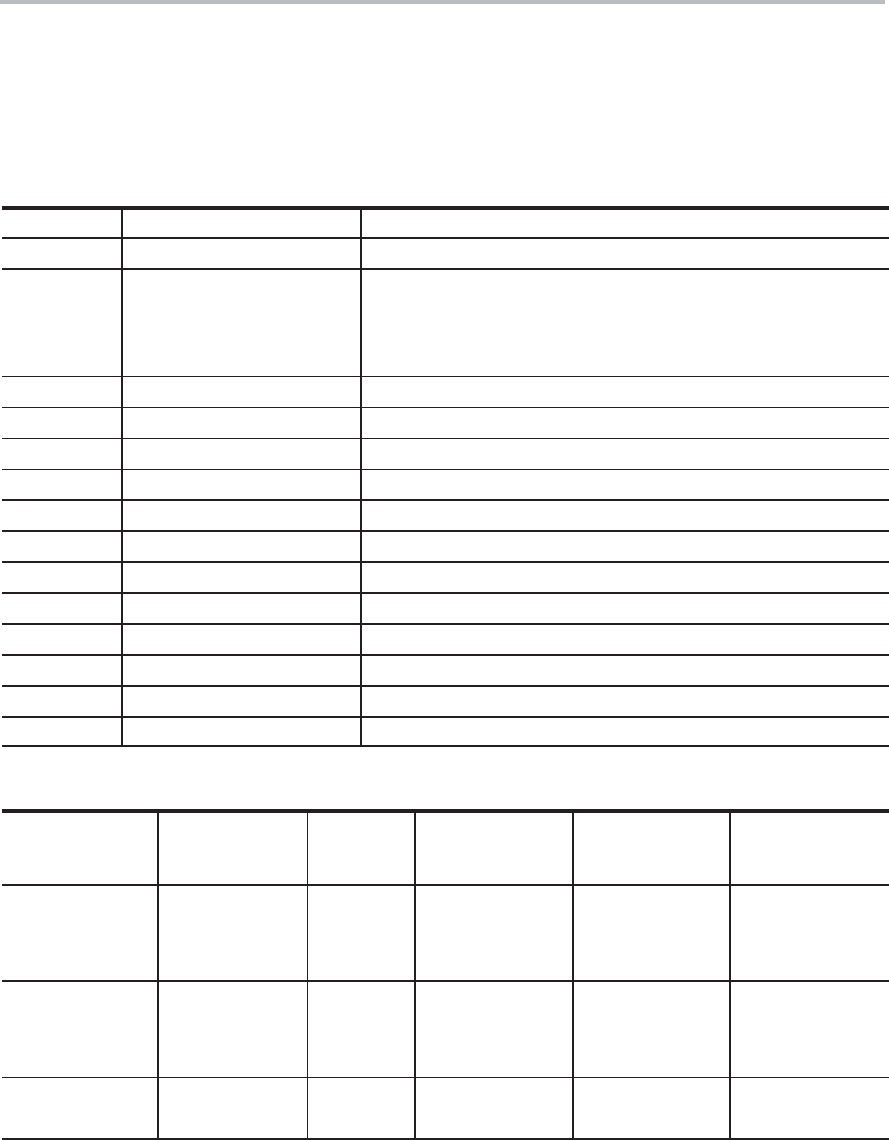

Table 2−7.J51 Pin Description

Pin Number Net-Name at Schematics Description

1 GND Ground

2 MCLK Master clock input. Low jitter system clock for PWM generation

and reclocking.

Ground connection from source to TAS5066 must be a low im-

pedance connection.

3 GND Ground

4 SDIN1 I2S data 1, channels 1 and 2

5 SDIN2 I2S data 2, channels 3 and 4

6 SDIN3 I2S data 3, channels 5 and 6

7−9 − Reserved

10 GND Ground

11 SCLK I2S bit clock

12 GND Ground

13 LRCLK I2S left-right clock

14 GND Ground

15 − Reserved

16 GND Ground

Table 2−8.Clock Rates

Speed TAS5066 System

Control Register

0 (x02h)

Sample

Frequency

(F

S

)

LRCLK SCLK (64xF

S

) MCLK

Normal speed

MCLK = 256xF

S

D7 = 0

D6 = 0

32 kHz

44.1 kHz

48 kHz

32.0 kHz

44.1 kHz

48.0 kHz

2.0480 MHz

2.8224 MHz

3.0720 MHz

8.1920 MHz

11.2896 MHz

12.2880 MHz

Double speed

MCLK = 256xF

S

D7 = 0

D6 = 1

64 kHz

88 kHz

96 kHz

64.0 kHz

88.2 kHz

96.0 kHz

4.0960 MHz

5.6448 MHz

6.1440 MHz

16.3840 MHz

22.5792 MHz

24.5760 MHz

Quad speed

MCLK = 128xF

S

D7 = 1

D6 = 0

176 kHz

192 kHz

176.4 kHz

192.0 kHz

11.2896 MHz

12.2880 MHz

22.5790 MHz

24.5760 MHz