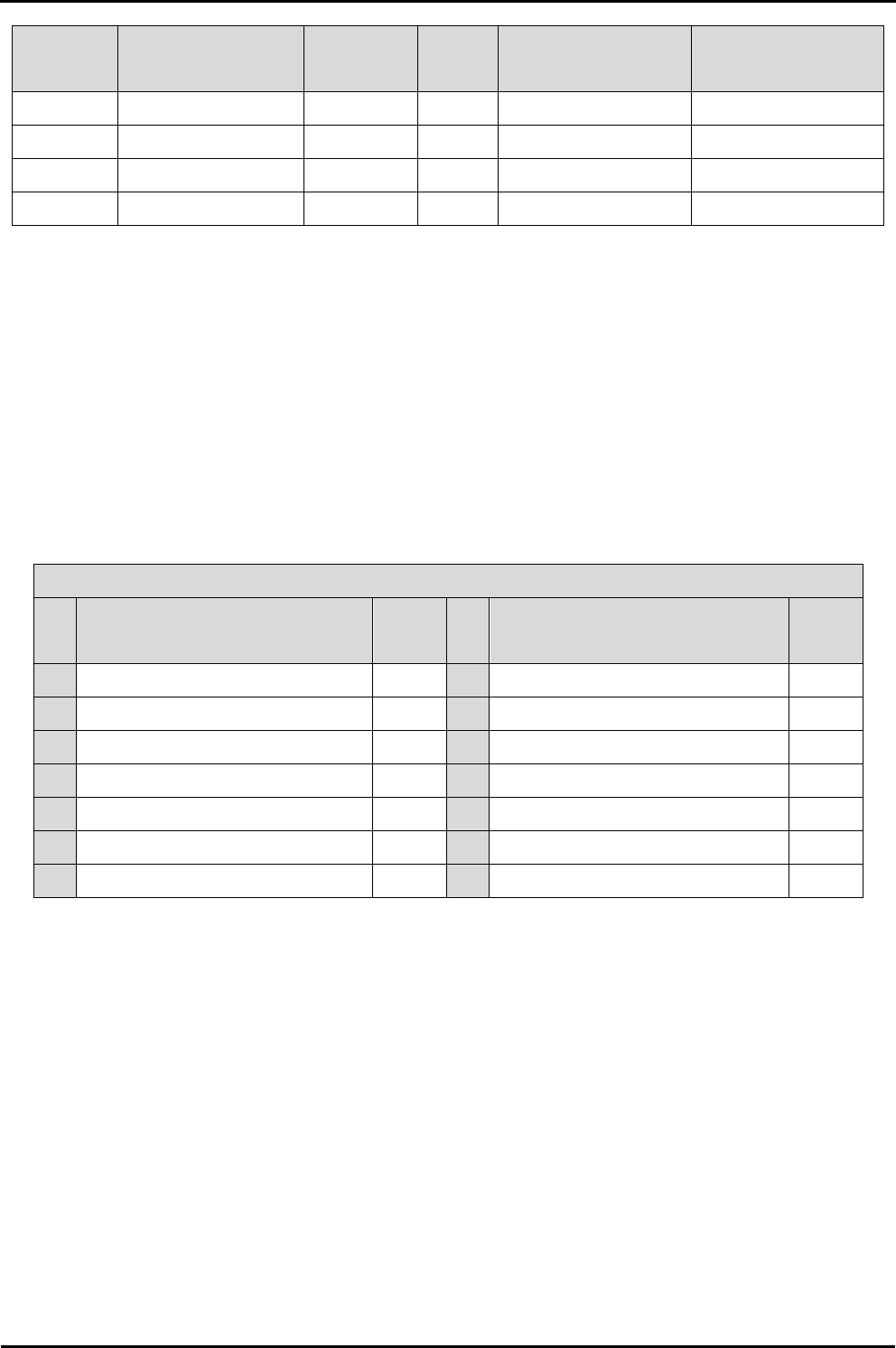

Description Function Circuit Net

Name

CPU’s

Pin

Fit for RS232 Remove for RS232

SCI0 Default serial port TXD0 52 R31 R37

SCI0 Default serial port RXD0 51 R30 R36

SCI5 Spare Serial Port TXD5 93 R34, R15 -

SCI5 Spare Serial Port RXD5 94 R35, R28 -

Table 6-3: Serial Port settings

The SCI0 port is also available on J2 and JA2 (R59 and R70 must be fitted) headers. The SCI5 port is available on J3 and JA6 headers..

6.5. Debug LCD Module

A debug LCD module is supplied to be connected to the connector marked ‘LCD’, so that the debug LCD module lies over J2. Care should

be taken to ensure the pins are inserted correctly into LCD. The debug LCD module uses a 4 bit interface to reduce the pin allocation. No

contrast control is provided; this is set by a resistor on the supplied display module. The module supplied with the RSK only supports 5V

operation.

Table 6-4 shows the pin allocation and signal names used on this connector.

LCD

Pin Circuit Net Name Device

Pin

Pin Circuit Net Name Device

Pin

1 Ground - 2 5V Only -

3 No Connection - 4

DLCDRS (PA0)

134

5 R/W (Wired to Write only) - 6

DLCDE + 100k pull down to ground (PA2)

136

7 No Connection - 8 No connection -

9 No Connection - 10 No connection -

11

DLCDD4 (PB4)

130

12

DLCDD5 (PB5)

131

13

DLCDD6 (PB6)

132

14

DLCDD7 (PB7)

5

Table 6-4 Debug LCD Module Connections

6.6.Option Links

Table 6-5 below describes the function of the option links contained on this RSK board and associated with Serial Port Configuration. The

default configuration is indicated by BOLD text.

11