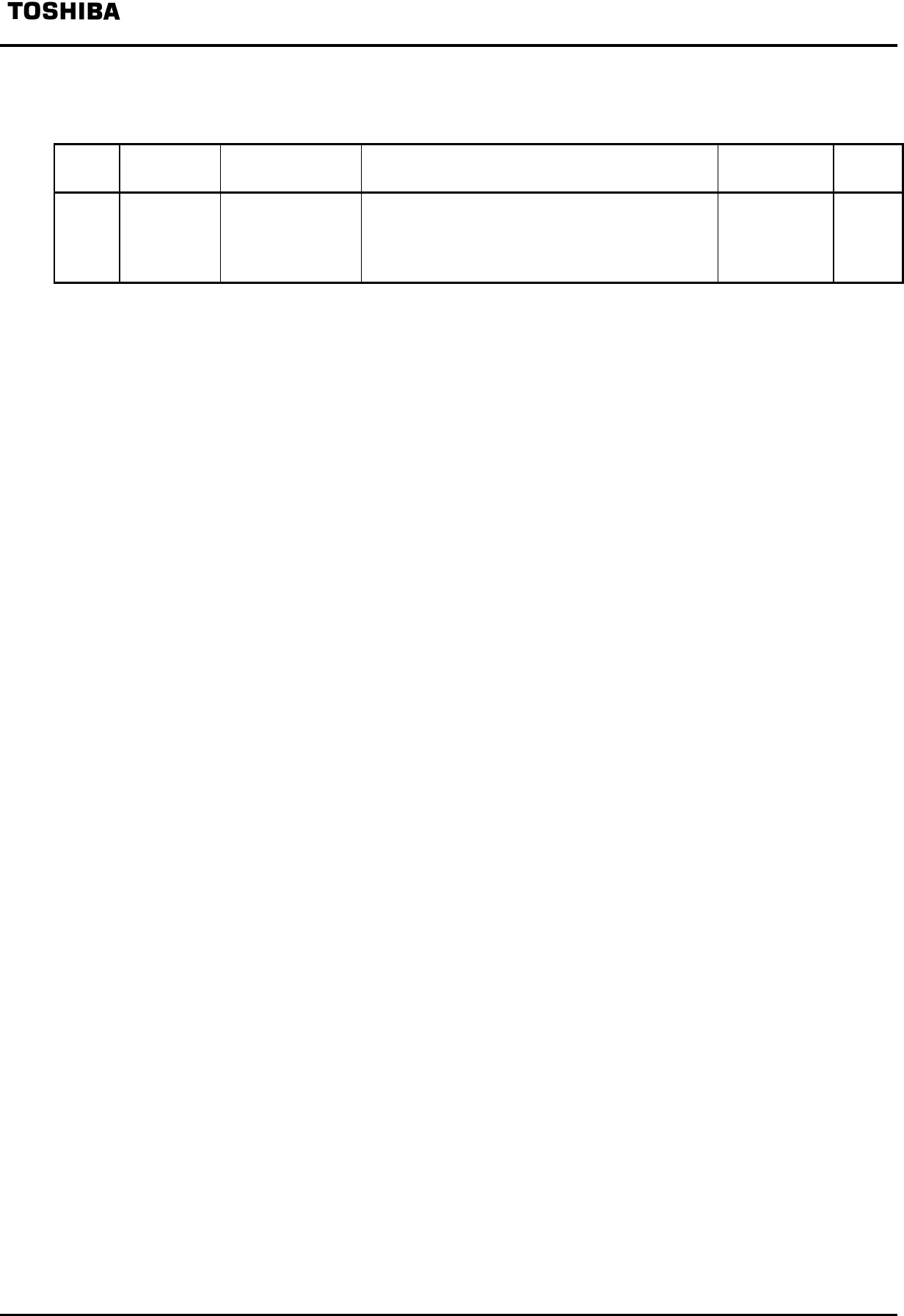

Architecture

55

Bits Mnemonic Field name Description

Value on

Reset

Read/

Write

27-26

24-23

19-16

7-6

0 Ignored on write; 0 when read. 0 Read

Figure 6-4. Status register (2/2)

(1) CU (Coprocessor Usability)

The CU bits CU0 - CU3 control the usability of the four coprocessors CP0 through CP3.

Setting a bit to 1 allows the corresponding coprocessor to be used, and clearing the bit to 0

disables that coprocessor. When an instruction for a coprocessor operation is used, the CU

bit for that coprocessor must be set; otherwise a Coprocessor Unusable exception will be

raised. Note that when the R3900 Processor Core is operating in kernel mode, the system

control coprocessor CP0 is always usable regardless of how CU0 is set.

(2) RE (Reverse Endian)

The RE bit determines whether big endian or little endian format is used when the processor is

initialized after a Reset exception. This bit is valid only in user mode; setting it to 1 reverses

the initial endian setting. In kernel mode the endian is always governed by the endian signal

set in a Reset exception. Since the RE bit status is undefined after a Reset exception, it

should be initialized by the Reset exception handler in kernel mode.

(3) TS (TLB Shutdown)

The TS bit is always 1.

(4) BEV (Bootstrap Exception Vector)

If the BEV bit is set to 1, then the alternate vector address is used for bootstrap when a UTLB

Refill exception or general exception occurs. If BEV is cleared to 0, the normal vector

address is used. Immediately after a Reset exception, BEV is set to 1.

The alternate vector address allows an exception to be raised to invoke a diagnostic test prior

to testing for normal operation of the cache and main memory systems.