CONCEPTSYSTEM EXAMPLESCONNECTIONSPRODUCTSBLOCK DIAGRAMS

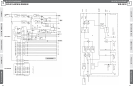

FPGA

SERIAL IN

SERIAL OUT

SERIAL CLK

MCK,BCK,WCK

SDT O SDT I

LCD I/F

MPX BUS

PARALLEL I/O

CPU

RTC

P/S

S/P

DIP

SW

LED

Flash MEM

SDRAM

GIPO

I2C

SPI

USB I/F

SD I/F

UART1

UART2

BATT

PLL

CN

CNCN

CNCNCN

27MHz

VCXO

3.3Vto5V

IF Switch

Local BUS

CORE Board

Main Board Panel Board

_~10

_~16

_~1

1234567812345678

1234567812345678

REC IN PHONES OUTPUT

SD

CODEC

P_FAIL

SENSE

MUTE

( Tr )

P/S

Digital Tr

Digital Tr

S/P

Rec

Input

Phones

Output

Announce

Message

Output

EMG

Message

Output

DC24V

5

4

Sirial IO

I/F between

the Amplifier

Parallel IO

12 Reg

5V Reg

5V Reg

3.3V Reg

CN

EMG

77

5

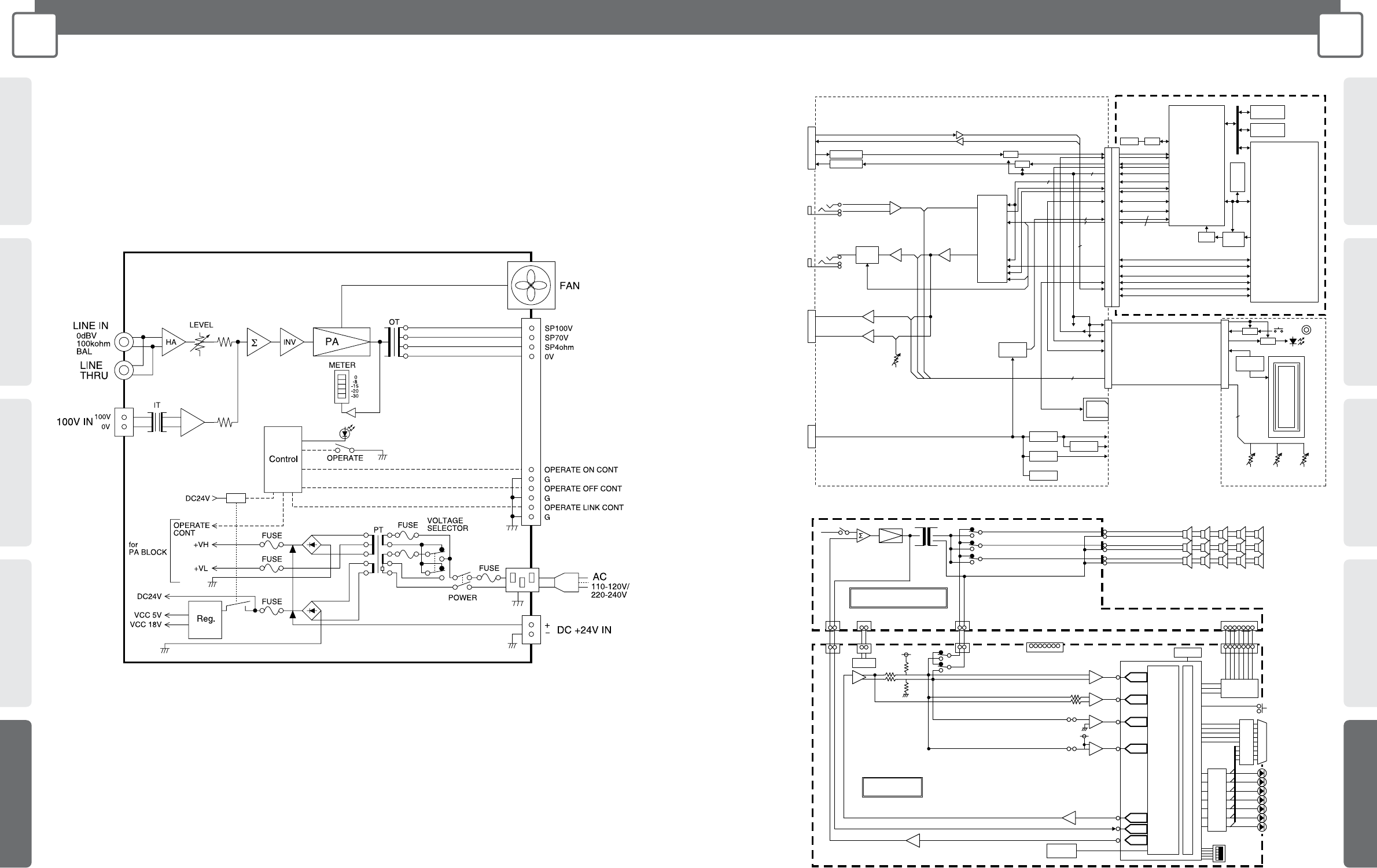

BLOCK DIAGRAMS

WU-ZM001E/WU-ZS001E

CONCEPT SYSTEM EXAMPLES CONNECTIONS PRODUCTS BLOCK DIAGRAMS

WU-ZM001E

Internal control

ADC0

ADC1

ADC2

ADC3

IOport

IOport

IOport

LPF

LPF

LPF

LPF

LPF

E2PROM

CPU

Serial

Pallarel

Check SW

SURVEILLANCE I/F

(D-sub25p)

Status

ZONE1

ZONE2

ZONE3

ZONE4

ZONE5

Grand Fault

DIP SW

Zone1

Zone2

Zone3

OPEN

Reset IC

DC24V Power

WU-ZS001E

Surveillance Unit

Speaker line

Pilot Signal

PA

Pilot Signal

PA

AMP

DC/DC

Audio announcement

OT

Serial Port, IO Port

Buffer

D-Tr

D-Tr

LPF

Reference Data

WA-MA120N or WA-MA240N

Mixing Power Amplifier

WU-ZS001E

76

5

BLOCK DIAGRAMS

WA-BA240N