What are SHARC Processors?

1-6 Getting Started With SHARC Processors

First generation SHARC products offer performance of up to

66 MHz/198 MFLOPS and form the cornerstone of the SHARC proces-

sor family. Their easy-to-use instruction set architecture that supports

both 32-bit fixed-point and 32/40-bit floating-point data formats, com-

bined with large memory arrays and sophisticated communications ports,

make them suitable for a wide array of parallel processing applications

including consumer audio, medical imaging, military, industrial, and

instrumentation.

Second generation SHARC products double the level of signal processing

performance (100 MHz/600 MFLOPS) by utilizing a single-instruction,

multiple-data (SIMD) architecture. This hardware extension doubles the

number of computational resources available to the system programmer.

Second generation products contain dual multipliers, ALUs, shifters, and

data register files, significantly increasing overall system performance in a

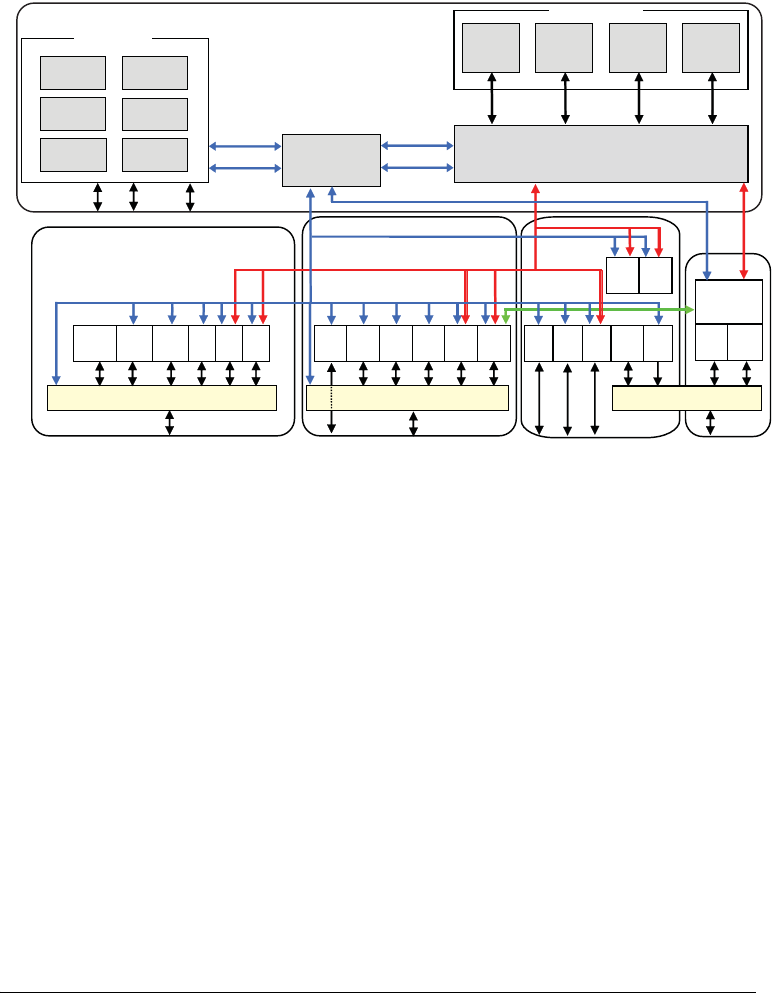

Figure 1-1. ADSP-2147x Processor Block Diagram

Internal Memory I/F

Block 0

RAM/ROM

B0D

64-BIT

Instruction

Cache

5Stage

Sequencer

PEx PEy

PMD

64-BIT

IOD0 32-BIT

EPD BUS 64-BIT

Core Bus

Cross Bar

S/PDIF

Tx/Rx

PCG

A

-

D

DPI Routing/Pins

SPI/B UART

Block 1

RAM/ROM

Block 2

RAM

Block 3

RAM

AMI

SDRAM

CTL

EP

External Port Pin MUX

TIMER

1

-

0

SPORT

7

-

0

ASRC

3

-

0

PWM

3

-

0

DAG1/2

Core

Timer

PDAP/

IDP

7

-

0

TWI

IOD0 BUS

DTCP/

MTM

PCG

C

-

D

PERIPHERAL BUS

32-BIT

CORE

FLAGS/

PWM3

-

1

JTAG

Internal Memory

DMD

64-BIT

PMD 64-BIT

CORE

FLAGS

IOD1

32-BIT

PERIPHERAL BUS

B1D

64-BIT

B2D

64-BIT

B3D

64-BIT

DPI Peripherals

DAI Peripherals

Peripherals

External

Port

SIMD Core

S

THERMAL

DIODE

FFT

FIR

IIR

MLB

SPEP BUS

DMD

64-BIT

FLAGx/IRQx/

TMREXP

WDT

RTC

SHIFT

REG

DAI Routing/Pins