www.ti.com

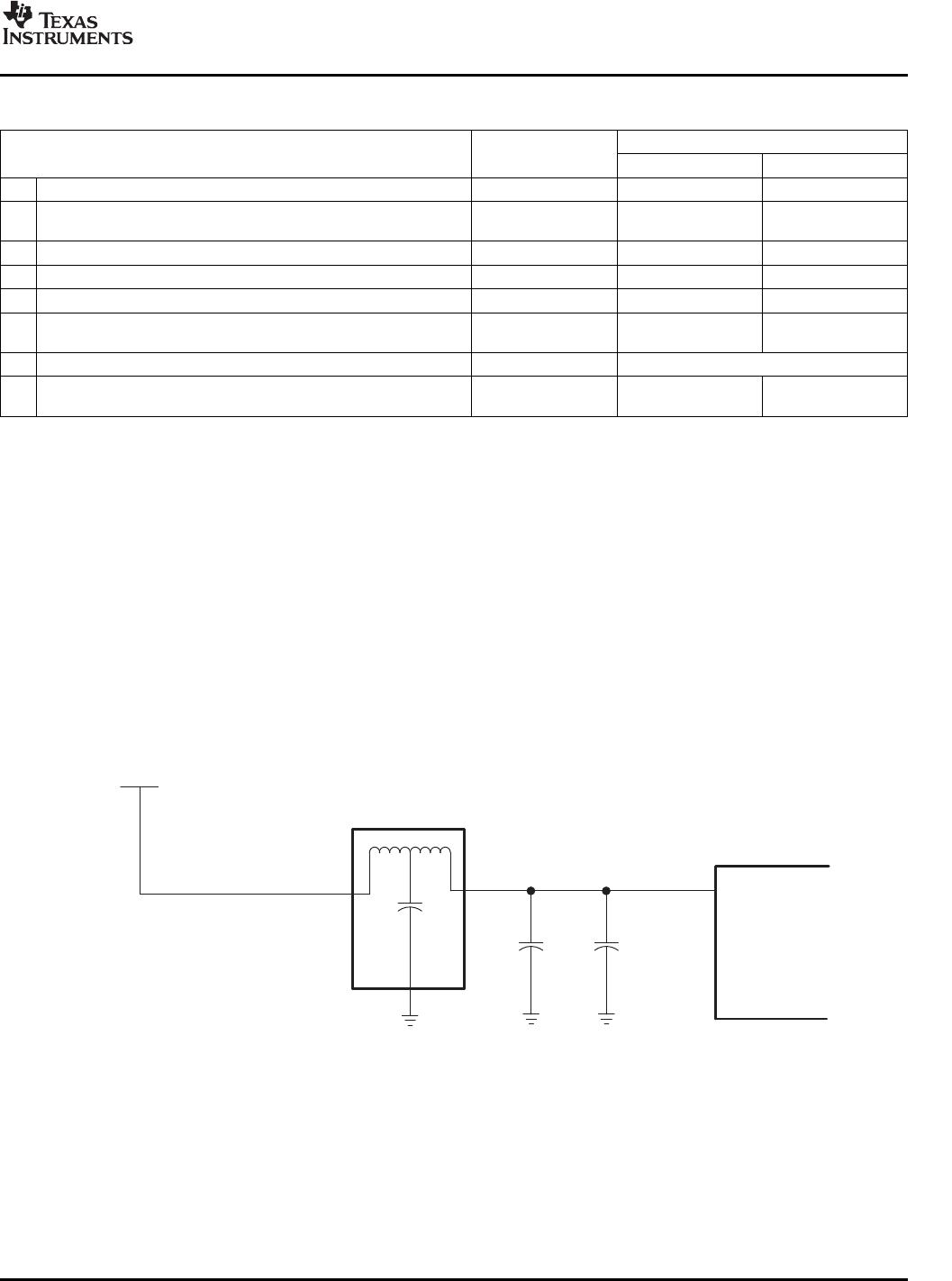

BOARD

DV

DD

(3.3 V)

EMI

Filter

10 mF 0.1 mF

PLLHV

Place Filter and Capacitors as Close

to DSP as Possible

EMI Filter: TDK ACF451832−333, −223, −153, or −103,

Panasonic EXCCET103U, or Equivalent

+

TMS320C6727,TMS320C6726,TMS320C6722

Floating-PointDigitalSignalProcessors

SPRS268E–MAY2005–REVISEDJANUARY2007

Table4-40.AllowedPLLOperatingConditions

ALLOWEDSETTINGORRANGE

PARAMETERDEFAULTVALUE

MINMAX

1PLLRST=1assertiontimeduringinitializationN/A125ns

2LocktimebeforesettingPLLEN=1.AfterchangingD0,PLLM,orN/A187.5µs

inputclock.

3PLLinputfrequency(PLLREFafterD0

(1)

)12MHz50MHz

4PLLmultipliervalues(PLLM)x13x4x25

5PLLoutputfrequency(PLLOUTbeforedividersD1,D2,D3)

(2)

N/A140MHz600MHz

6SYSCLK1frequency(setbyPLLManddividersD0,D1)PLLOUT/1DeviceFrequency

Specification

7SYSCLK2frequency(setbyPLLManddividersD0,D2)PLLOUT/2/2,/3,or/4ofSYSCLK1

8SYSCLK3frequency(setbyPLLManddividersD0,D3)PLLOUT/3EMIFFrequency

Specification

(1)SomevaluesfortheD0dividerproduceresultsoutsideofthisrangeandshouldnotbeselected.

(2)Ingeneral,selectingthePLLoutputclockrateclosesttothemaximumfrequencywilldecreaseclockjitter.

CAUTION

SYSCLK1,SYSCLK2,SYSCLK3mustbeconfiguredasalignedbysettingALNCTL[2:0]

to'1';andthePLLCMD.GOSETbitmustbewritteneverytimethedividersD1,D2,and

D3arechangedinordertomakesurethechangetakeseffectandpreserves

alignment.

CAUTION

WhenchangingthePLLparameterswhichaffecttheSYSCLK1,SYSCLK2,SYSCLK3

dividers,thebridgeBR2inFigure2-4mustberesetbytheCFGBRIDGEregister.See

Table2-7.

ThePLLisananalogcircuitandissensitivetopowersupplynoise.Thereforeithasadedicated3.3-V

powerpin(PLLHV)thatshouldbeconnectedtoDV

DD

attheboardlevelthroughanexternalfilter,as

illustratedinFigure4-44.

Figure4-44.PLLPowerSupplyFilter

SubmitDocumentationFeedbackPeripheralandElectricalSpecifications103