1 2 3 4 56

A

B

C

D

6

54321

D

C

B

A

ti

12500 TI Boulevard. Dallas, Texas 75243

TITLE:

SHEET: OF:

FILE: SIZE:

REV:

Drawn By:

Engineer:

Revision History

REV ECN Number Approved

DOCUMENT CONTROL #:

33

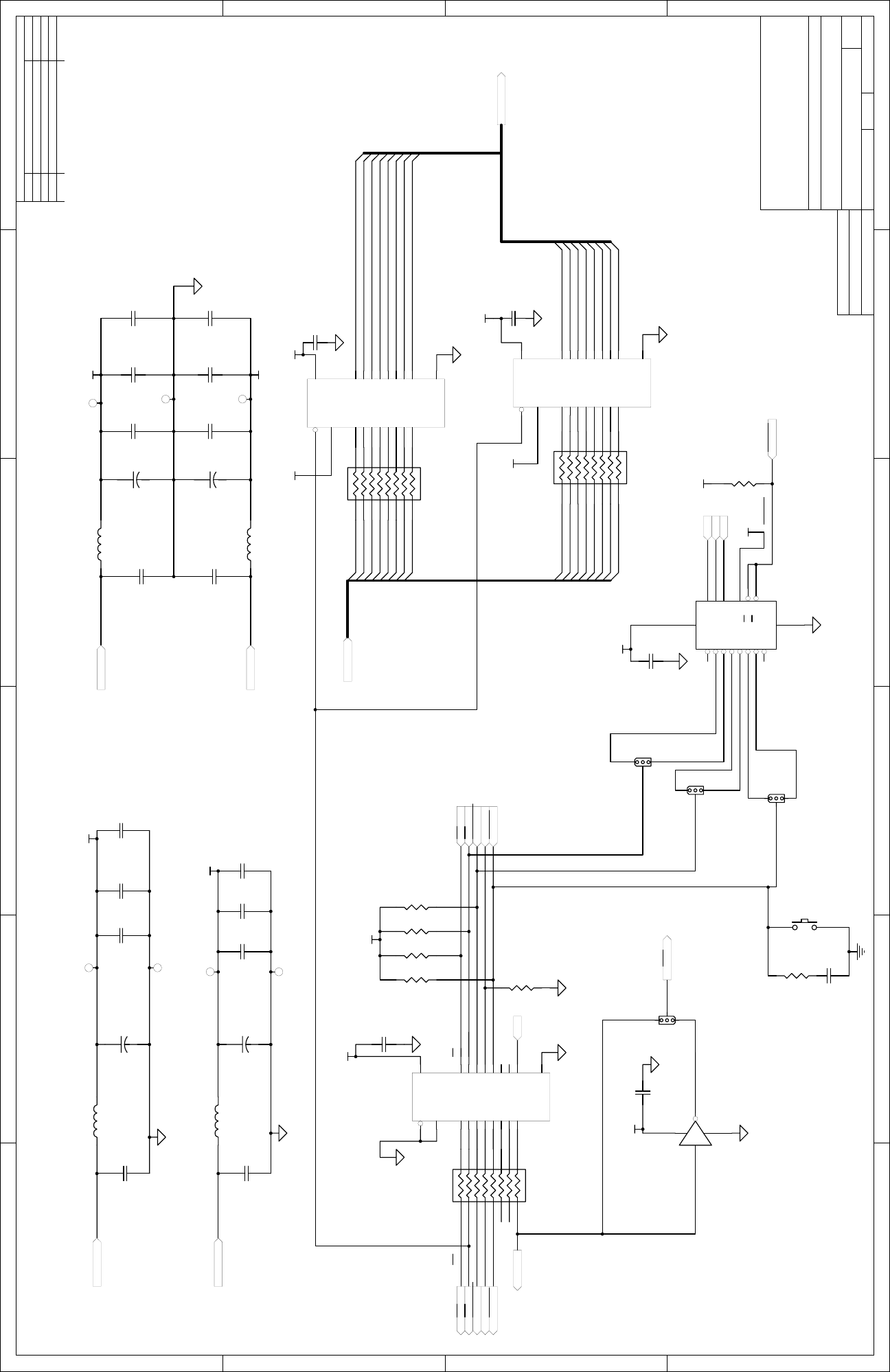

Power & Digital Buffer

A

DATE: 22-Oct-2003

Power Supply & Digital Buffer Circuit

6446998

L4

BLM21AJ601SN1L

L2

BLM21AJ601SN1L

L1

BLM21AJ601SN1L

C28

1uF

C2

1uF

C4

0.01uF

C26

0.01uF

L3

BLM21AJ601SN1L

TP6

+5VCC

C10

0.01uF

C9

0.1uF

TP5

TP8

+VBD

C20

0.01uF

C22

0.1uF

TP7

TP3

TP1

TP2

+VCC

-VCC

C12

10uF

C19

10uF

C6

10uF

C1

10uF

C5

1nF

C3

1nF

C23

1nF

C11

1nF

B_DB[17...0]

1 16

2 15

3 14

4 13

5

9

12

6

8

10

11

7

RP1

1K

+VBD

/OE

DIR

A1

A2

A3

A4

A5

A6

A7

A8

B1

B2

B3

B4

B5

B6

B7

B8

VCC

GND

U6

SN74AHC245PWR

+VBD

C57

0.1uF

1 16

2 15

3 14

4 13

5

9

12

6

8

10

11

7

RP3

1K

+VBD

/OE

DIR

A1

A2

A3

A4

A5

A6

A7

A8

B1

B2

B3

B4

B5

B6

B7

B8

VCC

GND

U7

SN74AHC245PWR

+VBD

C58

0.1uF

DB[17...0]

DB15

DB14

DB13

DB12

DB11

DB10

DB9

DB8

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

B_DB15

B_DB14

B_DB13

B_DB12

B_DB11

B_DB0

B_DB10

B_DB1

B_DB9

B_DB2

B_DB8

B_DB3

B_DB7

B_DB4

B_DB6

B_DB5

CS

RD

CONVST

BYTE

RESET

B_BUSY

1 16

2 15

3 14

4 13

5

9

12

6

8

10

11

7

RP2

100

/OE

DIR

A1

A2

A3

A4

A5

A6

A7

A8

B1

B2

B3

B4

B5

B6

B7

B8

VCC

GND

U5

SN74AHC245PWR

+VBD

C25

0.1uF

CS

RD

CONVST

BYTE

RESET

R20

10k

R19

10k

R18

10k

+VBD

R17

10k

R16

10k

BUSY

B_CS

B_RD

B_CONVST

B_BYTE

B_RESET

+AVCC

+VA

-VA

DB[17...0]

B_DB[17...0]

+BVDD

B_CS

B_BYTE

B_CONVST

B_RD

B_RESET

+

C14

10uF

+

C24

10uF

+

C27

10uF

+

C29

10uF

A

1

B

2

C

3

G1

6

G2A

4

G2B

5

Y0

15

Y1

14

Y2

13

Y3

12

Y4

11

Y5

10

Y6

9

Y7

7

VCC

16

GND

8

U11

SN74AHC138PWR

A0

A1

A2

A0

A2

A1

+VBD

C63

0.1uF

+VBD

1

3

2

W2

1

3

2

W5

W4

2 4

53

U10

SN74AHC1G04DBV

+VBD

C64

0.1uF

W3

DC_CS

R24

10k

+VBD

RESET#

S1

R25

100

C66

0.01uF

INTc

DC_CS

Lijoy Philipose

Lijoy Philipose