9.2. Application Headers

Table 9-5 and Table 9-6 below show the standard application header connections. * Marked pins are subject to option links.

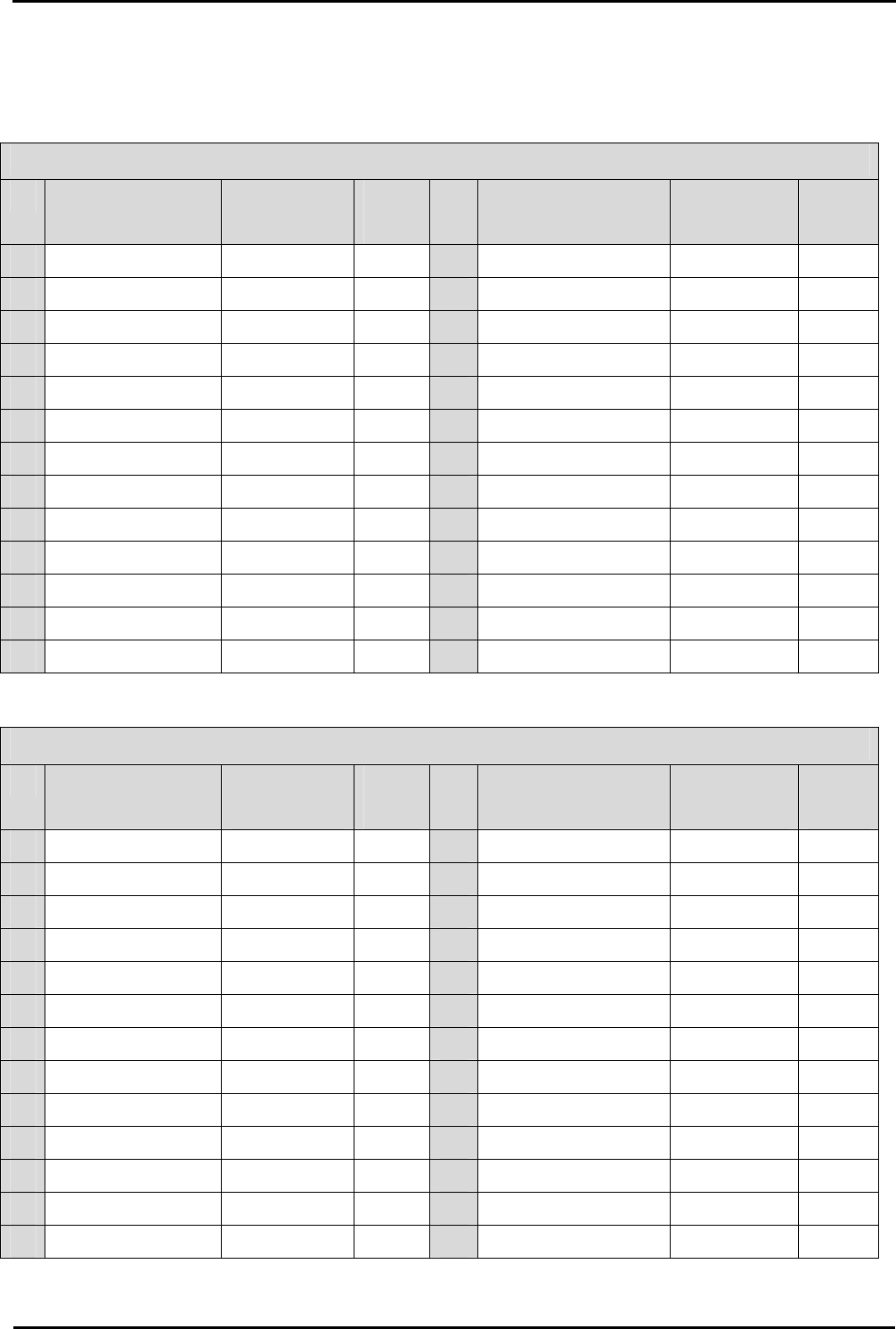

JA1

Pin Header Name RSK Signal

Name

Device

Pin

Pin Header Name RSK Signal

Name

Device

Pin

1 Regulated Supply 1 CON_5V - 2 Regulated Supply 1 GROUND -

3 Regulated Supply 2 CON_3V3 - 4 Regulated Supply 2 GROUND -

5 Analogue Supply NC - 6 Analogue Supply NC -

7 Analogue Reference CON_VREF 44 8 ADTRG NC -

9 ADC0 AD0 38 10 ADC1 AD1 41

11 ADC2 AD2 42 12 ADC3 AD3 43

13 DAC0 NC - 14 DAC1 NC -

15 IOPort0 IO_0 45 16 IOPort1 IO_1* 47

17 IOPort2 IO_2 46 18 IOPort3 IO_3 37

19 IOPort4 IO_4 36 20 IOPort5 IO_5 35

21 IOPort8 IO_6* 28 22 IOPort7 IO_7* 29

23 IRQ3 IRQ3 25 24 I

2

C Bus (3rd pin) NC -

25 I²C Bus IIC_SDA 4 26 I²C Bus IIC_SCL 2

Table 9-5: JA1 Standard Generic Header

JA2

Pin Header Name RSK Signal

Name

Device

Pin

Pin Header Name RSK Signal

Name

Device

Pin

1 Reset RESn 8 2 External Clock Input CON_XIN 11

3 Interrupt NC - 4 Regulated Supply 1 GND -

5 SPARE NC - 6 Serial Port SCIaTX 24

7 Interrupt IRQ0* 27 8 Serial Port SCIaRX 23

9 Interrupt IRQ1* 28 10 Serial Port SCIaCK 22

11 Motor up/down MO_UD* 52 12 Serial Port Handshake NC -

13 Motor control MO_Up 19 14 Motor control MO_Un 17

15 Motor control MO_Vp 16 16 Motor control MO_Vn 14

17 Motor control MO_Wp 15 18 Motor control MO_W 13

19 Timer Output TMR0 18 20 Timer Output TMR1 34

21 Timer Input TRIGa* 27 22 Timer Input TRIGb 21

23 Interrupt IRQ2* 29 24 Tristate Control TRISTn 3

25 SPARE P2_0 20 26 SPARE P3_1 33

Table 9-6: JA2 Standard Generic Header

16