14/24 SR-C8002 Rev.1.0

6.2.2.Timing of Host Interface (PIO)

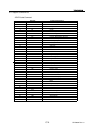

Figure 9 shows the Host Interface Timings

t1

t4

Address valid*1

DIOR-/DIOW-*1

Write data valid*1

t6

t7

Read data valid*1

IOCS16-*1

t8

IORDY

tRD

t6Z

t9

tA tB

t2i

t3

t5

t0

t2

*1: In all timing diagrams, the low line indicator negated, and the upper line

indicators asserted.

PIO timing parameters min (ns) max (ns) Min Time (ns) Max Time (ns)

t0 Cycle time 120

t1 Address valid to DIOR/DIOW-setup 25

t2 DIOR/DIOW-pulse wide 70

t2i DIOR/DIOW-recovery time 25

t3 DIOW-data setup 20

t4 DIOW-data hold 10

t5 DIOR-data setup 20

t6 DIOR-data hold 5

t6Z DIOR-data tristate 30

t7 Addr valid to IOCS 16-assertion 30

t8 Addr valid to IOCS 16-negation 30

t9 DIOR/DIOW-to address valid hold 10

tRD Read Data Valid to IORDY active 0

tA IORDY setup 35

tB IORDY pulse wide 1250

Figure 9 Host Interface Timing (PIO Mode4)