TMS320F2809, TMS320F2808, TMS320F2806

TMS320F2802, TMS320F2801, TMS320C2802

TMS320C2801, TMS320F28016, TMS320F28015

SPRS230L–OCTOBER 2003–REVISED DECEMBER 2009

www.ti.com

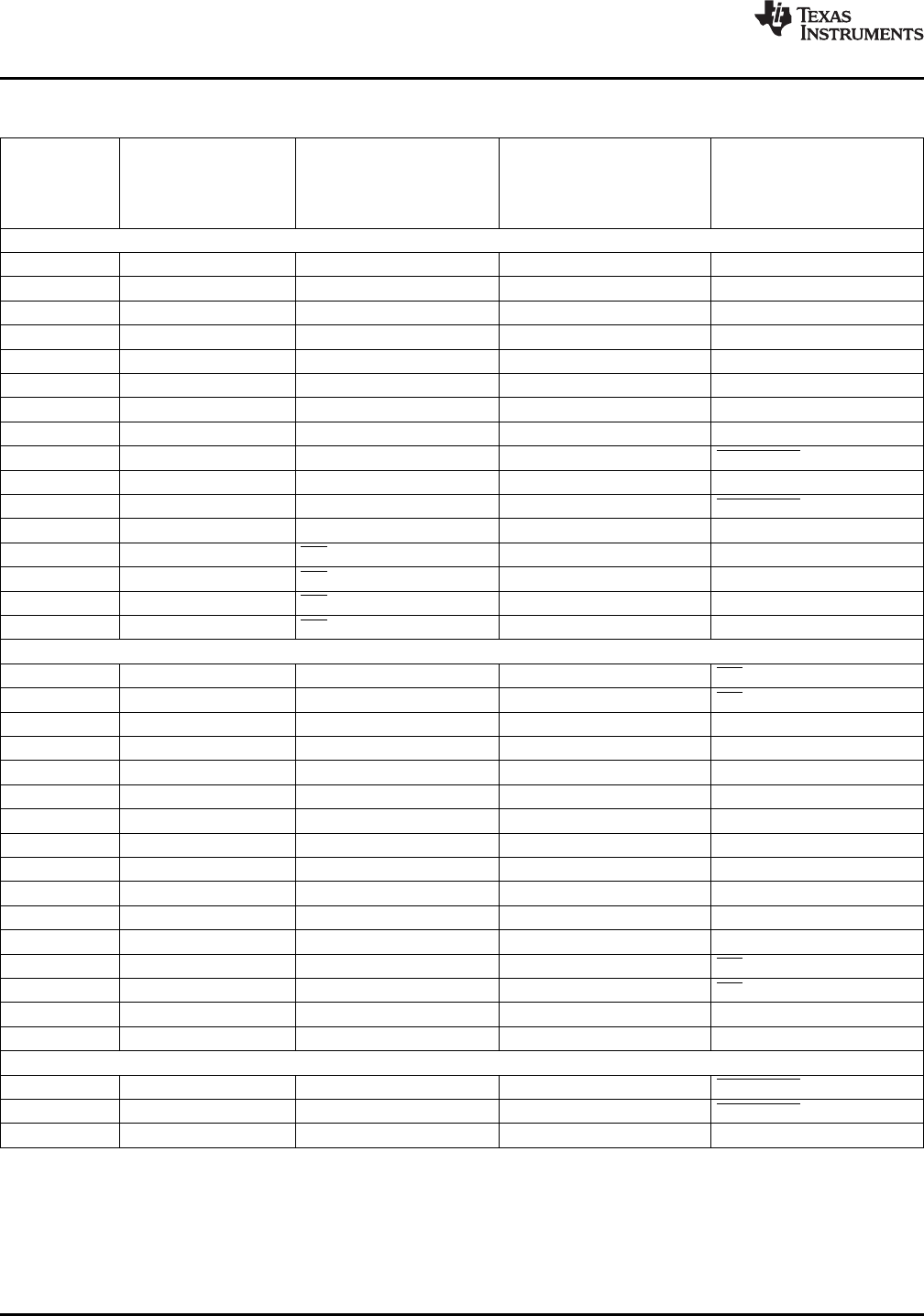

Table 4-16. F2808 GPIO MUX Table

DEFAULT AT RESET

GPAMUX1/2

(1)

PRIMARY I/O PERIPHERAL PERIPHERAL PERIPHERAL

REGISTER FUNCTION SELECTION 1

(2)

SELECTION 2 SELECTION 3

BITS (GPxMUX1/2 (GPxMUX1/2 BITS = 0,1) (GPxMUX1/2 BITS = 1,0) (GPxMUX1/2 BITS = 1,1)

BITS = 0,0)

GPAMUX1

1–0 GPIO0 EPWM1A (O) Reserved

(3)

Reserved

(3)

3–2 GPIO1 EPWM1B (O) SPISIMOD (I/O) Reserved

(3)

5–4 GPIO2 EPWM2A (O) Reserved

(3)

Reserved

(3)

7–6 GPIO3 EPWM2B (O) SPISOMID (I/O) Reserved

(3)

9–8 GPIO4 EPWM3A (O) Reserved

(3)

Reserved

(3)

11–10 GPIO5 EPWM3B (O) SPICLKD (I/O) ECAP1 (I/O)

13–12 GPIO6 EPWM4A (O) EPWMSYNCI (I) EPWMSYNCO (O)

15–14 GPIO7 EPWM4B (O) SPISTED (I/O) ECAP2 (I/O)

17–16 GPIO8 EPWM5A (O) CANTXB (O) ADCSOCAO (O)

19–18 GPIO9 EPWM5B (O) SCITXDB (O) ECAP3 (I/O)

21–20 GPIO10 EPWM6A (O) CANRXB (I) ADCSOCBO (O)

23–22 GPIO11 EPWM6B (O) SCIRXDB (I) ECAP4 (I/O)

25–24 GPIO12 TZ1 (I) CANTXB (O) SPISIMOB (I/O)

27–26 GPIO13 TZ2 (I) CANRXB (I) SPISOMIB (I/O)

29–28 GPIO14 TZ3 (I) SCITXDB (O) SPICLKB (I/O)

31–30 GPIO15 TZ4 (I) SCIRXDB (I) SPISTEB (I/O)

GPAMUX2

1–0 GPIO16 SPISIMOA (I/O) CANTXB (O) TZ5 (I)

3–2 GPIO17 SPISOMIA (I/O) CANRXB (I) TZ6 (I)

5–4 GPIO18 SPICLKA (I/O) SCITXDB (O) Reserved

(3)

7–6 GPIO19 SPISTEA (I/O) SCIRXDB (I) Reserved

(3)

9–8 GPIO20 EQEP1A (I) SPISIMOC (I/O) CANTXB (O)

11–10 GPIO21 EQEP1B (I) SPISOMIC (I/O) CANRXB (I)

13–12 GPIO22 EQEP1S (I/O) SPICLKC (I/O) SCITXDB (O)

15–14 GPIO23 EQEP1I (I/O) SPISTEC (I/O) SCIRXDB (I)

17–16 GPIO24 ECAP1 (I/O) EQEP2A (I) SPISIMOB (I/O)

19–18 GPIO25 ECAP2 (I/O) EQEP2B (I) SPISOMIB (I/O)

21–20 GPIO26 ECAP3 (I/O) EQEP2I (I/O) SPICLKB (I/O)

23–22 GPIO27 ECAP4 (I/O) EQEP2S (I/O) SPISTEB (I/O)

25–24 GPIO28 SCIRXDA (I) Reserved

(3)

TZ5 (I)

27–26 GPIO29 SCITXDA (O) Reserved

(3)

TZ6 (I)

29–28 GPIO30 CANRXA (I) Reserved

(3)

Reserved

(3)

31–30 GPIO31 CANTXA (O) Reserved

(3)

Reserved

(3)

GPBMUX1

1–0 GPIO32 SDAA (I/OC) EPWMSYNCI (I) ADCSOCAO (O)

3–2 GPIO33 SCLA (I/OC) EPWMSYNCO (O) ADCSOCBO (O)

5–4 GPIO34 Reserved

(3)

Reserved

(3)

Reserved

(3)

(1) GPxMUX1/2 refers to the appropriate MUX register for the pin; GPAMUX1, GPAMUX2 or GPBMUX1.

(2) This table pertains to the 2808 device. Some peripherals may not be available in the 2809, 2806, 2802, or 2801 devices. See the pin

descriptions for more detail.

(3) The word "Reserved" means that there is no peripheral assigned to this GPxMUX1/2 register setting. Should it be selected, the state of

the pin will be undefined and the pin may be driven. This selection is a reserved configuration for future expansion.

84 Peripherals Copyright © 2003–2009, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320F2809 TMS320F2808 TMS320F2806 TMS320F2802 TMS320F2801 TMS320C2802

TMS320C2801 TMS320F28016 TMS320F28015